Hi all,

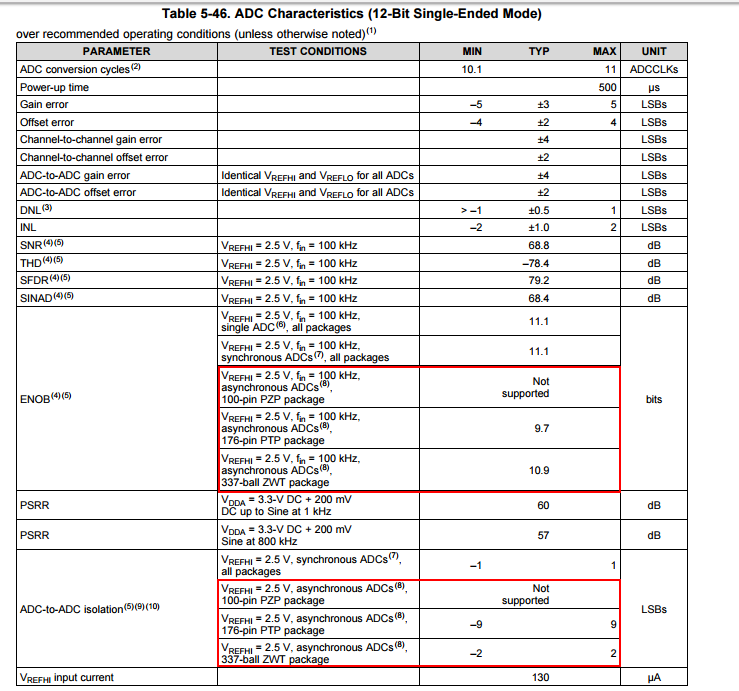

We are working on the F28379D Delfino part 337 ball grid. The requirement is to sample 3 phase voltages and currents with simultaneous V/I pairs in 16 bit mode. I am a bit confused about the 4 ADC modules in the Delfino so please confirm if this scheme works as expected. The trigger source is timer0 for all SOCs. SOC0 should trigger sampling for Va and Ia simultanesouly, SOC1 Vb, Ib and SOC2 Vc and Ic.

Differential Inputs Module SOC

Va C2, C3 C 0

Ia D0, D1 D 0

Vb C4, C5 C 1

Ib D2, D3 D 1

Vc B4, B5 B 2

Ic D4, D5 D 2 <- last conversion

Also, in the spruhm8f there is a mention of SOCC and SOCD, is it a typo?

Thanks in advance