Hello

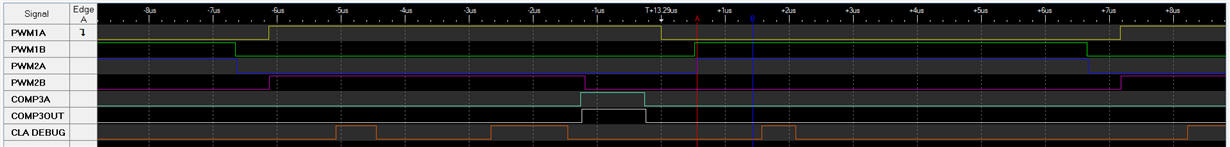

I'm trying to setup a blanking window on TMS320F28035. I have a CBC trip zone configured from COMP3 to trip PWM2. I want the blanking window to start right at the beginning of the pwm period and last over the dead time and until some time after the pulse starts. But if I set DCOFFSET to 0 it seems that a trip at the very end of a period can trip the next pulse before the blanking window is activated causing the whole pulse to disappear.

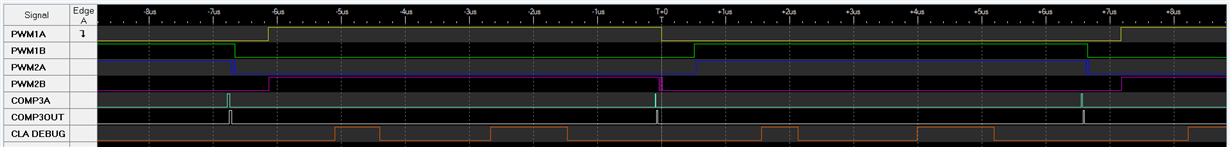

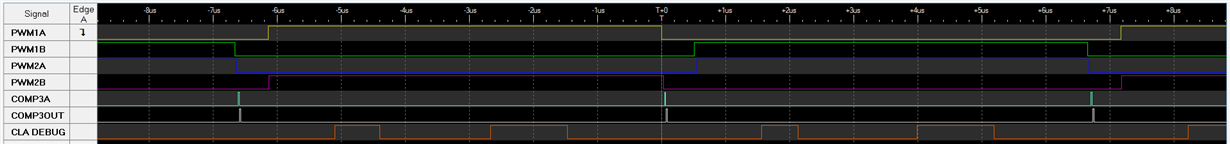

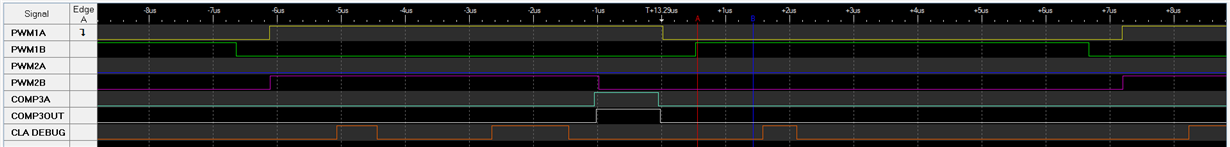

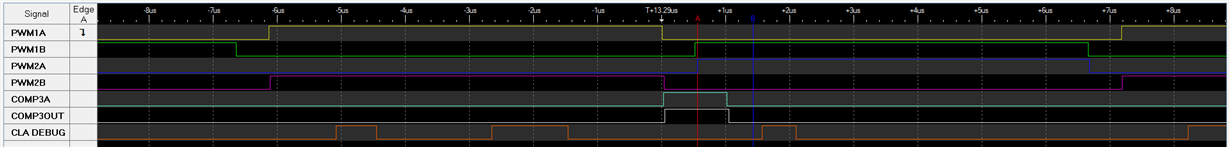

For testing I use a spare pwm connected to COMP3A and generate a sweeping pulse to see how the trip zone acts at different timings. On the first image the PWM2A and B pulses are still tripped normally but when I advance the test pulse right one step (second image) the PWMs are tripped before they have begun.

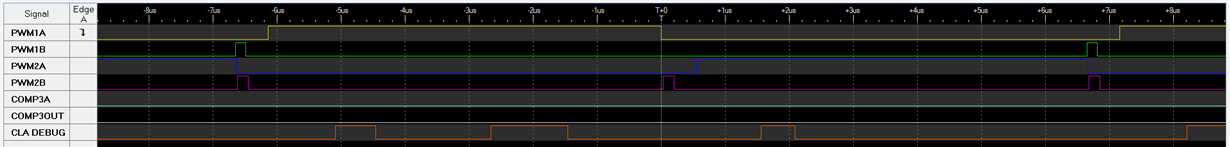

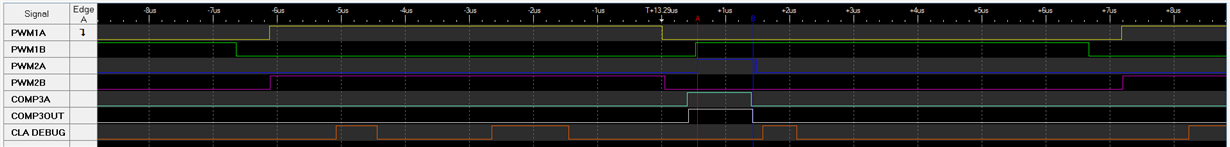

After advancing a few steps more (third image) the blanking window starts to work correctly and PWM2 pulses are started even if there is a trip during the dead time.

As a workaround, I can set the offset to TBPRD - 5 so that the blanking window actually starts from the end of the previous cycle, but I'm confused why it doesn't work with offset 0 as expected? The CBC trip should be cleared at the end of the period and it should not be possible to trip the next pulse? Or are there some other delays on the trip signal that I don't know of?

Best regards

Pauli