Tool/software: Code Composer Studio

Hi Ti Community,

i have a question about the Digital Compare Submodule in the TMS32F28035.

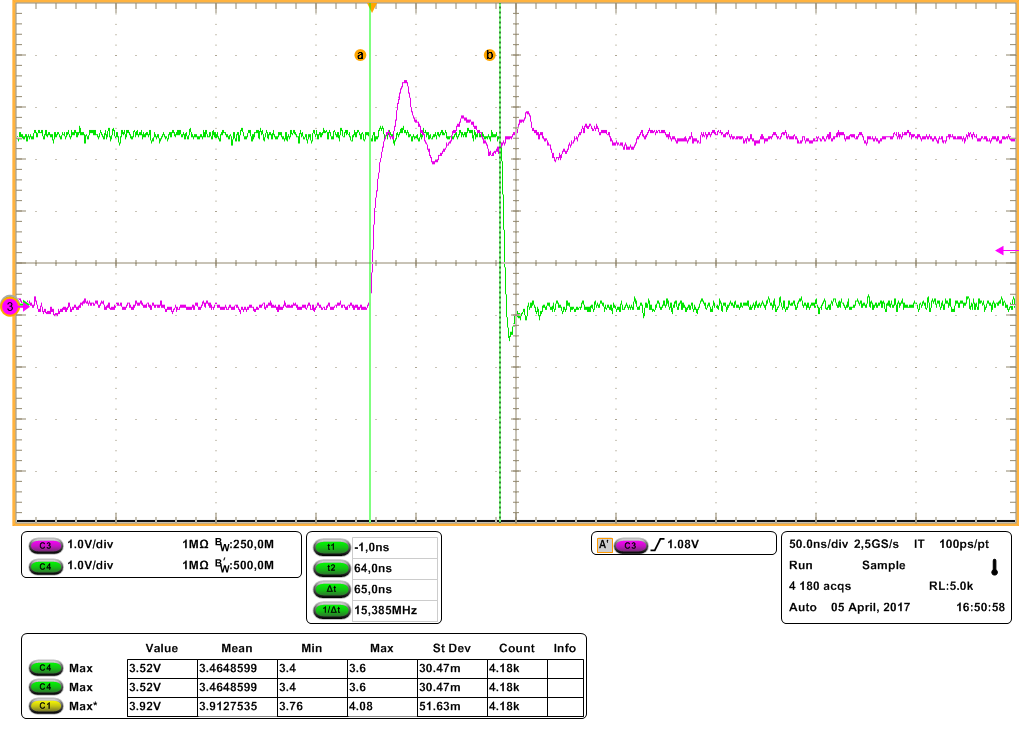

The pink waveform in the attached screenshot is the EPwm1A signal, which is turned on throught the Trip Zone Submodule triggered by the TZ1 input.

The green waveform is turned of throught the Action Qualifier Submodule. So the DCAEVT1 sync the TBCTR to zero, and the CMPA register is zero so the EPWm2A output get low.

But i have a fixed delay of about 65 ns. Is there any way to decrease this delay? I can't turn EPwm2A on by the TripZone Module because I need a dead band between this two signals.

Tobias Ofenberger