Hi there,

I am using the ADC module in the DSP 28377D, in Single ended mode, 12-bit resolution. I wanted to ask you if you could help confirming that my adc configuration is correct.

1. Each ADC is configure as follow:

void ConfigureADC_A(void)

{

EALLOW;

//write configurations

AdcaRegs.ADCCTL2.bit.PRESCALE = 0;

AdcSetMode(ADC_ADCA, ADC_RESOLUTION_12BIT, ADC_SIGNALMODE_SINGLE);

//Set pulse positions to late

AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1;

//power up the ADC

AdcaRegs.ADCCTL1.bit.ADCPWDNZ = 1;

//delay for 1ms to allow ADC time to power up

DELAY_US(1000);

EDIS;

}

the question here is: by setting

AdcaRegs.ADCCTL2.bit.PRESCALE = 0;

knowing that in my program I have set

ClkCfgRegs.PERCLKDIVSEL.bit.EPWMCLKDIV = 0

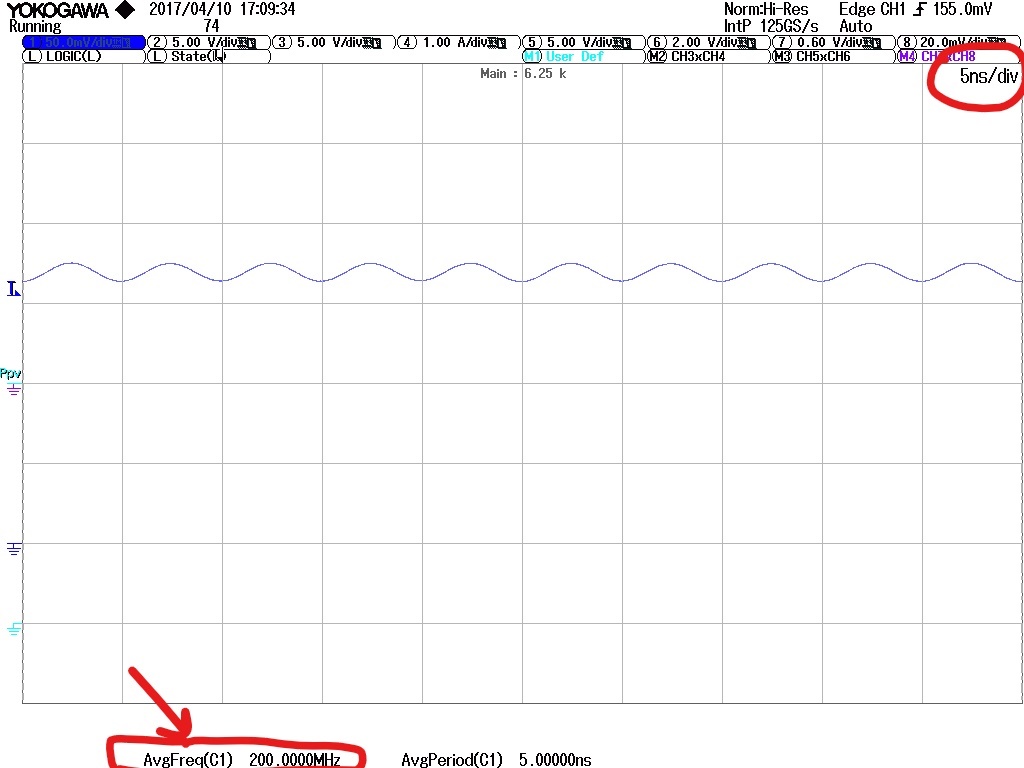

does it mean that the 1x ADC CLOCK period is = SYSCLK/1= (200MHz)^-1 = 5ns? this seems very small.

2. I need to confirm that the calculation of the ADC parameter ACQPS is correct.

I can see that in the SPRUHM8C (pag. 1221) document TI gives a guideline on how to roughly estimate the acquisition window time "t":

where the T on the right is the charging time constant of the sample and hold capacitor.

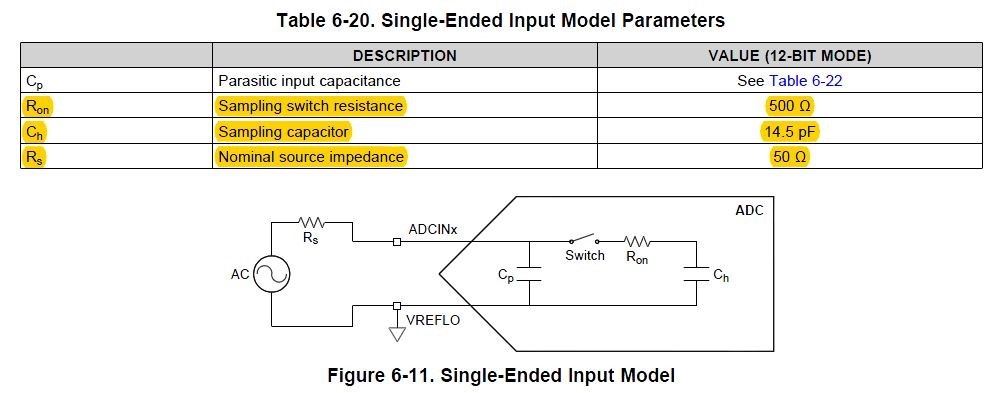

Based on the recommendations in SPRUHM8C (pag. 1221) and the model of the ADC reported in the datasheet SPRS880C (p. 107, reported below)

then:

T = (Rs+Ron)*Ch.

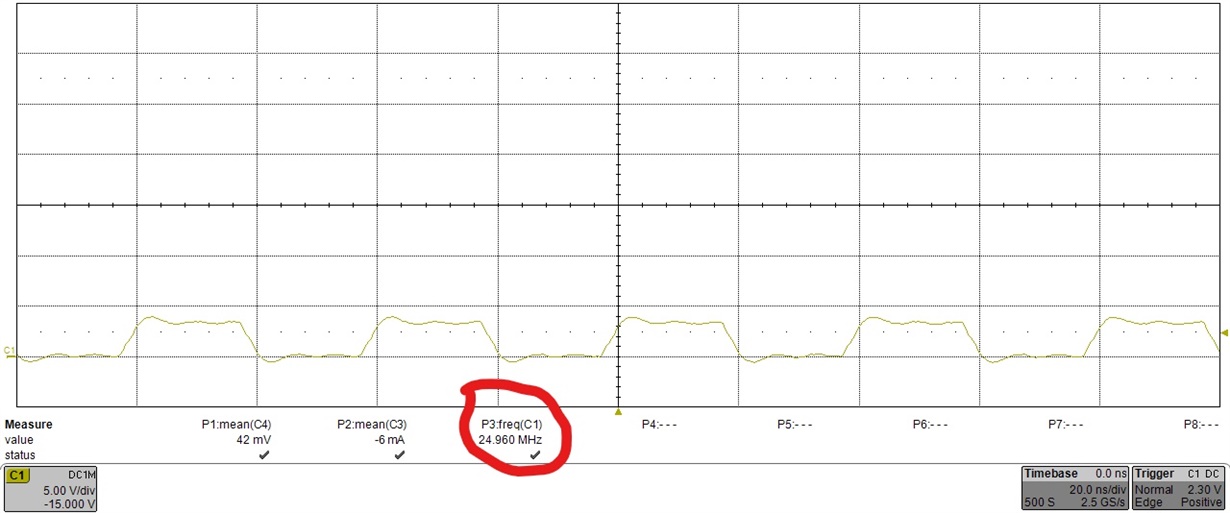

Now, in my case the ADC input is connected to the output of an op-amp via a 200 Ohm resistor, like in the picture below

My question is, should I consider Rs = 200Ohm then? If so, I calculate T = (500+200Ohm)*14.5pF=10*10^-9s and the acquisition window time t = -ln(0.25/2^12)*T=100ns.

Having, t=100ns=(ACQPS+1)*SYSCLK --> ACQPS = 100ns/5ns - 1 =19 (where SYSCLK=5ns, as the clock is 200MHz).

In summary, I came up with:

1. one ADC CLK = 5ns, as

AdcaRegs.ADCCTL2.bit.PRESCALE = 0

2. ACQPS = 19, considering Rs=200Ohm (the resistance between the adc input and the op-amp output) and Ch and Ron given in the datasheet SPRS880C (p. 107).

Could you please confirm if my reasoning is correct? Especially in regards to point 2, and the Rs I consider for the calculation of the acquisition window.

Thank you very much for your time.

Leo