Part Number: TMS320F28069

Other Parts Discussed in Thread: C2000WARE

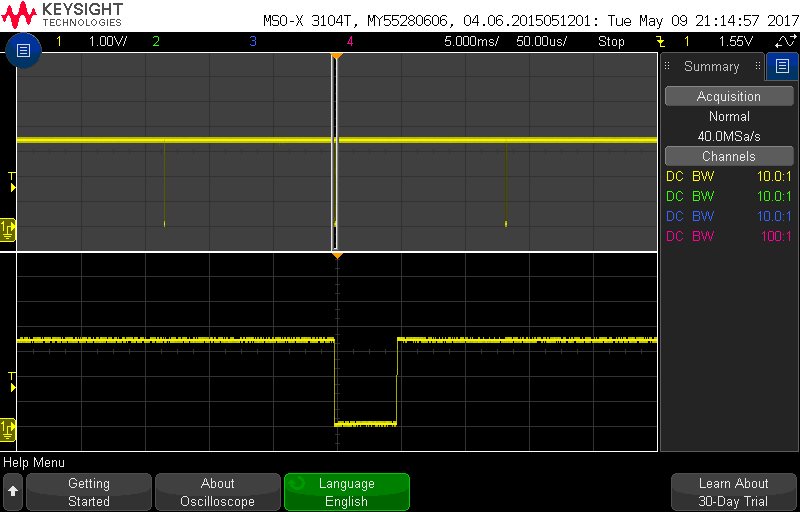

Device is powered correctly with clean 3.3V uses internal 1.8V also very clean yet XRS is issuing a reset every 14mS. Pulse is 50uS wide. All connections follow datasheet recommendations but because of this the JTAG cannot connect.