Part Number: F28M35H52C

Other Parts Discussed in Thread: CONTROLSUITE

Hi all,

My application requires data exchange between Master controller cortex m3 and control subsystem c2000 controller on concerto family of controllers. So I am trying to understand the example provided for F28M35H52C series on Control suite.

The example i am referring to reside in this below location:

/home/user_name/controlSUITE/device_support/f28m35x/v208/F28M35x_examples_Dual/Internal_Loopback_Serial

&

/home/preetham/controlSUITE/device_support/f28m35x/v208/F28M35x_examples_Dual/mtoc_ipcdrivers

As i am new in to development of concerto series controllers, i need some help with understanding these above examples. So I have decided to ask few questions regarding the same.

1. This is directed towards the Internal_Loopback_Serial example from control suite. There is a very small description which says this will send some data from cortex m3 and the data if received on c2000 will be echoed back to m3.

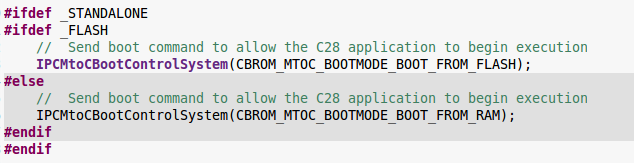

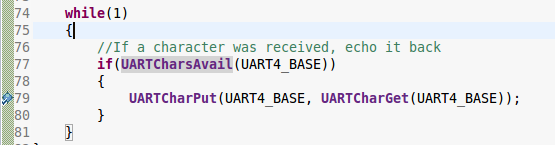

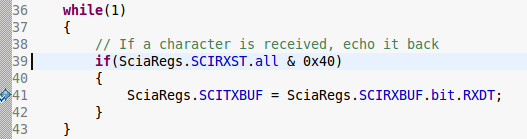

But when i place a breakpoint inside the below code the program never stops here both in m3 and c2000. can anyone please help me figure what am i missing ? So if i make it work how can i verify if the data is exchanged between the cores ? Also to mention i choose to run the c2000 from flash like shown below, not sure if this fine for this example ?

The below code snippets are from internalLB_UART.c and internalLB_SCI.c files

2. This is directed towards mtoc_ipcdrivers example, The example describes that it shoes all the API's that can be used to communicate between m3 and c2000 cores using IPC and shared RAM.

But when i ran this example i see that from project mtoc_ipc_drivers_m3 it writes the data from m3 to c2000 and reads back that same data from c2000 using different available option and i was interested in

// Data Block Writes section from mtoc_ipcdrivers_m3.c file.

Now my question is how can i modify this example such that from mtoc_ipc_drivers_c28 project i want to write some data in to C2000 part of the S0 SARAM memeory and read this data back on m3 controller from mtoc_ipc_drivers_m3 project ? I have attached two source files which i tried to edit and run but with no success. (Attached files are : mtoc_ipc_drivers_m3.c & mtoc_ipc_drivers_c28.c )

//###########################################################################

//

// FILE: mtoc_ipcdrivers_m3.c

//

// TITLE: MtoC IPC Drivers (M3) Example

//

//! \addtogroup dual_example_list

//! <h1>Master to Control IPC Drivers (mtoc_ipcdrivers)</h1>

//!

//! This example application demonstrates the use of the M3 to C28

//! IPC Driver Functions which allow the M3 to read/write to

//! addresses on the C28 or read values from the C28 into

//! addresses on the M3. CtoM MSG RAM and MtoC MSG RAM are used to

//! store the IPC Driver buffers and indexes and also to pass the addresses

//! of local variables between the processors.

//!

//! \b Build \b Configurations:

//! - RAM,FLASH - Run and debug application from either RAM or FLASH memory

//! - RAM,FLASH Standalone - Run application as standalone (CCS debugger not

//! connected). Application automatically runs from

//! either RAM or FLASH after boot-up.

//!

//

//###########################################################################

// $TI Release: F28M35x Support Library v208 $

// $Release Date: Tue Sep 6 09:31:30 CDT 2016 $

// $Copyright: Copyright (C) 2011-2016 Texas Instruments Incorporated -

// http://www.ti.com/ ALL RIGHTS RESERVED $

//###########################################################################

#include "inc/hw_ints.h"

#include "inc/hw_memmap.h"

#include "inc/hw_types.h"

#include "inc/hw_memmap.h"

#include "inc/hw_nvic.h"

#include "inc/hw_types.h"

#include "inc/hw_sysctl.h"

#include "inc/hw_ram.h"

#include "inc/hw_ipc.h"

#include "driverlib/debug.h"

#include "driverlib/gpio.h"

#include "driverlib/interrupt.h"

#include "driverlib/sysctl.h"

#include "driverlib/cpu.h"

#include "driverlib/ipc.h"

#include "driverlib/ram.h"

#include "utils/ustdlib.h"

//*****************************************************************************

// The error routine that is called if the driver library encounters an error.

//*****************************************************************************

#ifdef DEBUG

void

__error__(char *pcFilename, unsigned long ulLine)

{

}

#endif

//*****************************************************************************

// Definitions used in this example

//*****************************************************************************

#define M3_CTOM_PASSMSG 0x2007F7E8 // CTOM MSG RAM offsets for

// passing addresses

#define SETMASK_16BIT 0xFF00 // Mask for setting bits of

// 16-bit word

#define CLEARMASK_16BIT 0xA5A5 // Mask for clearing bits of

// 16-bit word

#define SETMASK_32BIT 0xFFFF0000 // Mask for setting bits of

// 32-bit word

#define CLEARMASK_32BIT 0xA5A5A5A5 // Mask for clearing bits of

// 32-bit word

#define M3_S0SARAM_START 0x20008000 // Start of S0 SARAM in M3

// memory map

//*****************************************************************************

// Function Prototypes

//*****************************************************************************

void Error(void);

void CtoMIPC1IntHandler(void);

void CtoMIPC2IntHandler(void);

//*****************************************************************************

// At least 1 volatile global tIpcController instance is required when using

// IPC API Drivers.

//*****************************************************************************

volatile tIpcController g_sIpcController1;

volatile tIpcController g_sIpcController2;

//*****************************************************************************

// Global variable used in this example to track errors

//*****************************************************************************

volatile unsigned short ErrorFlag;

volatile unsigned short ErrorCount;

//*****************************************************************************

// Global variables used in this example to read/write data passed between

// M3 and C28

//*****************************************************************************

unsigned short usWWord16;

unsigned long ulWWord32;

unsigned short usRWord16;

unsigned long ulRWord32;

unsigned short usMBuffer[128] = {741, 974, 2345, 764, 331, 456, 321, 989};

//*****************************************************************************

// Main Function

//*****************************************************************************

void

main(void)

{

// Define Local Variables

unsigned short counter;

unsigned short *pusMBufferPt;

unsigned short *pusCBufferPt;

unsigned long *pulMsgRam;

// Setup main clock tree for 75MHz - M3 and 150MHz - C28x

SysCtlClockConfigSet(SYSCTL_SYSDIV_1 | SYSCTL_M3SSDIV_2 | SYSCTL_USE_PLL |

(SYSCTL_SPLLIMULT_M & 0x0F));

// Initialize M3toC28 message RAM and Sx SARAM and wait until initialized

RAMMReqSharedMemAccess(S0_ACCESS, SX_M3MASTER);

//

// Allow writes to protected registers.

//

HWREG(SYSCTL_MWRALLOW) = 0xA5A5A5A5;

//

// Initialize S0 RAM and MtoC MSG RAM Used by Example

//

HWREG(RAM_CONFIG_BASE + RAM_O_MSXRTESTINIT1) |= 0x1;

while((HWREG(RAM_CONFIG_BASE + RAM_O_MSXRINITDONE1)&0x1) != 0x1)

{

}

HWREG(RAM_CONFIG_BASE + RAM_O_MTOCCRTESTINIT1) |= 0x1;

while((HWREG(RAM_CONFIG_BASE + RAM_O_MTOCRINITDONE)&0x1) != 0x1)

{

}

// Disable writes to protected registers.

HWREG(SYSCTL_MWRALLOW) = 0;

// Register M3 interrupt handlers

IntRegister(INT_CTOMPIC1, CtoMIPC1IntHandler);

IntRegister(INT_CTOMPIC2, CtoMIPC2IntHandler);

// Disable Clocking to Watchdog Timer1 and Watchdog Timer0

SysCtlPeripheralDisable(SYSCTL_PERIPH_WDOG0);

SysCtlPeripheralDisable(SYSCTL_PERIPH_WDOG1);

//#ifdef _STANDALONE

#ifdef _FLASH

// Send boot command to allow the C28 application to begin execution

IPCMtoCBootControlSystem(CBROM_MTOC_BOOTMODE_BOOT_FROM_FLASH);

#else

// Send boot command to allow the C28 application to begin execution

IPCMtoCBootControlSystem(CBROM_MTOC_BOOTMODE_BOOT_FROM_RAM);

#endif

//#endif

// Initialize IPC Controllers

IPCMInitialize (&g_sIpcController1, IPC_INT1, IPC_INT1);

IPCMInitialize (&g_sIpcController2, IPC_INT2, IPC_INT2);

// Enable processor interrupts.

IntMasterEnable();

// Enable the IPC interrupts.

IntEnable(INT_CTOMPIC1);

IntEnable(INT_CTOMPIC2);

// Initialize local variables

pulMsgRam = (void *)M3_CTOM_PASSMSG;

pusMBufferPt = (void *)M3_S0SARAM_START;

pusCBufferPt = (void *)(M3_S0SARAM_START + 128);

ErrorCount = 0;

//for (counter = 0; counter < 128; counter++)

//{

//usMBuffer[counter] = ((counter<<8)+(~counter));

//}

usWWord16 = 0x1234;

ulWWord32 = 0xABCD5678;

usRWord16 = 0;

ulRWord32 = 0;

// Spin here until C28 has written variable addresses to pulMsgRam

while ((HWREG(MTOCIPC_BASE + IPC_O_CTOMIPCSTS) & IPC_CTOMIPCSTS_IPC17) !=

IPC_CTOMIPCSTS_IPC17)

{

}

HWREG(MTOCIPC_BASE + IPC_O_CTOMIPCACK) = IPC_CTOMIPCACK_IPC17;

/*// 16 and 32-bit Data Writes

// Write 16-bit word to C28 16-bit write word variable.

IPCMtoCDataWrite(&g_sIpcController1, pulMsgRam[0],(unsigned long)usWWord16,

IPC_LENGTH_16_BITS, ENABLE_BLOCKING,

NO_FLAG);

// Read 16-bit word from C28 16-bit write word variable. Use IPC Flag 17 to

// check when read data is ready.

IPCMtoCDataRead(&g_sIpcController1, pulMsgRam[0], &usRWord16,

IPC_LENGTH_16_BITS, ENABLE_BLOCKING,

IPC_FLAG17);

// Write 32-bit word to C28 32-bit write word variable.

IPCMtoCDataWrite(&g_sIpcController1, pulMsgRam[1],ulWWord32,

IPC_LENGTH_32_BITS, ENABLE_BLOCKING,

NO_FLAG);

// Read 32-bit word from C28 32-bit write word variable. Use IPC Flag 18 to

// check when read data is ready.

IPCMtoCDataRead(&g_sIpcController1, pulMsgRam[1], &ulRWord32,

IPC_LENGTH_32_BITS, ENABLE_BLOCKING,

IPC_FLAG18);

// Wait until read variables are ready (by checking IPC Response Flag is

// cleared). Then check Read var = Write var

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC17)

{

}

if (usWWord16 != usRWord16)

{

ErrorCount++;

}

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC18)

{

}

if (ulWWord32 != ulRWord32)

{

ErrorCount++;

}*/

/*// 16 and 32-bit Data Set Bits

// Set upper 8 bits in 16-bit write word variable location.

IPCMtoCSetBits(&g_sIpcController1, pulMsgRam[0],

(unsigned long)SETMASK_16BIT, IPC_LENGTH_16_BITS,

ENABLE_BLOCKING);

// Read 16-bit word from C28 16-bit write word variable. Use IPC Flag 17 to

// check when read data is ready.

IPCMtoCDataRead(&g_sIpcController1, pulMsgRam[0], &usRWord16,

IPC_LENGTH_16_BITS, ENABLE_BLOCKING,

IPC_FLAG17);

// Set upper 16 bits in 32-bit write word variable location.

IPCMtoCSetBits(&g_sIpcController1, pulMsgRam[1], SETMASK_32BIT,

IPC_LENGTH_32_BITS,

ENABLE_BLOCKING);

// Read 32-bit word from C28 32-bit write word variable. Use IPC Flag 18 to

// check when read data is ready.

IPCMtoCDataRead(&g_sIpcController1, pulMsgRam[1], &ulRWord32,

IPC_LENGTH_32_BITS, ENABLE_BLOCKING,

IPC_FLAG18);

// Wait until read variables are ready (by checking IPC Response Flag is

// cleared). Then check correct bits are set.

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC17)

{

}

if (usRWord16 & SETMASK_16BIT != SETMASK_16BIT)

{

ErrorCount++;

}

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC18)

{

}

if (ulRWord32 & SETMASK_32BIT != SETMASK_32BIT)

{

ErrorCount++;

}*/

/*// 16 and 32-bit Data Clear Bits

// Clear alternating bits in 16-bit write word variable location

IPCMtoCClearBits(&g_sIpcController1, pulMsgRam[0],

(unsigned long)CLEARMASK_16BIT, IPC_LENGTH_16_BITS,

ENABLE_BLOCKING);

// Read 16-bit word from C28 16-bit write word variable. Use IPC Flag 17 to

// check when read data is ready.

IPCMtoCDataRead(&g_sIpcController1, pulMsgRam[0], &usRWord16,

IPC_LENGTH_16_BITS, ENABLE_BLOCKING,

IPC_FLAG17);

// Clear alternating bits in 32-bit write word variable location

IPCMtoCClearBits(&g_sIpcController1, pulMsgRam[1],

(unsigned long)CLEARMASK_32BIT, IPC_LENGTH_32_BITS,

ENABLE_BLOCKING);

// Read 16-bit word from C28 32-bit write word variable. Use IPC Flag 18 to

// check when read data is ready.

IPCMtoCDataRead(&g_sIpcController1, pulMsgRam[1], &ulRWord32,

IPC_LENGTH_32_BITS, ENABLE_BLOCKING,

IPC_FLAG18);

// Wait until read variables are ready (by checking IPC Response Flag is

// cleared). Then check correct bits are clear.

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC17)

{

}

if ((usRWord16 & (~CLEARMASK_16BIT)) != usRWord16)

{

ErrorCount++;

}

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC18)

{

}

if ((ulRWord32 & (~CLEARMASK_32BIT) ) != ulRWord32)

{

ErrorCount++;

}*/

// Data Block Writes

// Request Memory Access to S0 SARAM for M3

RAMMReqSharedMemAccess (S0_ACCESS, SX_M3MASTER);

while ((HWREG(RAM_CONFIG_BASE + RAM_O_MSXMSEL) & S0_ACCESS) != 0)

{

}

/* // Write a block of data from M3 to S0 shared RAM which is then written to a

// C28 address.

for (counter = 0; counter < 128; counter++)

{

pusMBufferPt[counter] = usMBuffer[counter];

}

IPCMtoCBlockWrite(&g_sIpcController2, pulMsgRam[2],

(unsigned long)pusMBufferPt, 128, IPC_LENGTH_16_BITS,

ENABLE_BLOCKING);

// Give Memory Access to S0 SARAM to C28

RAMMReqSharedMemAccess (S0_ACCESS, SX_C28MASTER);

while ((HWREG(RAM_CONFIG_BASE + RAM_O_MSXMSEL) & S0_ACCESS) != S0_ACCESS)

{

}

*/

// Read data back from C28.

IPCMtoCBlockRead(&g_sIpcController2, pulMsgRam[2],

(unsigned long)pusCBufferPt, 128, ENABLE_BLOCKING,

IPC_FLAG17);

// Wait until read data is ready (by checking IPC Response Flag is cleared).

// Then check for correct data.

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC17)

{

}

for (counter = 0; counter <128; counter++)

{

if (usMBuffer[counter] != pusCBufferPt[counter])

{

ErrorFlag = 1;

}

}

if (ErrorFlag == 1)

{

ErrorCount++;

}

/*// Check Function Call Function

// Call FunctionCall() function on C28 with a dummy parameter of "0"(i.e. no

// parameter).

IPCMtoCFunctionCall(&g_sIpcController1, pulMsgRam[3], 0, ENABLE_BLOCKING);

// Read status variable to check if function was entered. Use IPC Flag 17 to

// check when read data is ready.

IPCMtoCDataRead(&g_sIpcController1, pulMsgRam[5], &usRWord16,

IPC_LENGTH_16_BITS, ENABLE_BLOCKING,

IPC_FLAG17);

// Call FunctionCall() function on C28 with a parameter of "0x12345678".

IPCMtoCFunctionCall(&g_sIpcController1, pulMsgRam[4], 0x12345689,

ENABLE_BLOCKING);

// Read status variable to check if function was entered. Use IPC Flag 18 to

// check when read data is ready.

IPCMtoCDataRead(&g_sIpcController1, pulMsgRam[5], &ulRWord32,

IPC_LENGTH_32_BITS, ENABLE_BLOCKING,

IPC_FLAG18);

// Wait until read data is ready (by checking IPC Response Flag is cleared).

// Then check status variables to see if function was entered.

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC17)

{

}

if (usRWord16 != 1)

{

ErrorCount++;

}

while (HWREG(MTOCIPC_BASE + IPC_O_MTOCIPCFLG) & IPC_MTOCIPCFLG_IPC18)

{

}

if (ulRWord32 != 0x12345689)

{

ErrorCount++;

}*/

for(;;)

{

// When Complete, Loop Forever here.

}

}

//*****************************************************************************

// CtoM IPC INT1 Interrupt Handler -

// Handles writes into M3 addresses as a result of read commands to the C28.

//*****************************************************************************

void

CtoMIPC1IntHandler (void)

{

tIpcMessage sMessage;

// Continue processing messages as long as MtoC GetBuffer1 is full

while (IpcGet(&g_sIpcController1, &sMessage,

DISABLE_BLOCKING) != STATUS_FAIL)

{

switch (sMessage.ulcommand)

{

case IPC_DATA_WRITE:

IPCCtoMDataWrite(&sMessage);

break;

default:

ErrorFlag = 1;

break;

}

}

// Acknowledge IPC INT1 Flag

HWREG(MTOCIPC_BASE + IPC_O_CTOMIPCACK) |= IPC_CTOMIPCACK_IPC1;

}

//*****************************************************************************

// CtoM IPC INT2 Interrupt Handler -

// Should never reach this ISR. This is an optional placeholder for

// g_sIpcController2.

//*****************************************************************************

void

CtoMIPC2IntHandler (void)

{

// Should never reach here - Placeholder for Debug

// Acknowledge IPC INT2 Flag

HWREG(MTOCIPC_BASE + IPC_O_CTOMIPCACK) |= IPC_CTOMIPCACK_IPC2;

}

//###########################################################################

// FILE: mtoc_ipcdrivers_c28.c

// TITLE: 28M35x MtoC IPC Drivers (C28) Example

// ASSUMPTIONS:

// This program requires the 28M35x header files.

// As supplied, this project is configured for "boot to SARAM"

// operation. The 28M35x Boot Mode table is shown below.

// $Boot_Table

// While an emulator is connected to your device, the TRSTn pin = 1,

// which sets the device into EMU_BOOT boot mode. In this mode, the

// peripheral boot modes are as follows:

// Boot Mode: EMU_KEY EMU_BMODE

// (0xD00) (0xD01)

// ---------------------------------------

// Wait !=0x55AA X

// I/O 0x55AA 0x0000

// SCI 0x55AA 0x0001

// Wait 0x55AA 0x0002

// Get_Mode 0x55AA 0x0003

// SPI 0x55AA 0x0004

// I2C 0x55AA 0x0005

// OTP 0x55AA 0x0006

// Wait 0x55AA 0x0007

// Wait 0x55AA 0x0008

// SARAM 0x55AA 0x000A <-- "Boot to SARAM"

// Flash 0x55AA 0x000B

// Wait 0x55AA Other

// Write EMU_KEY to 0xD00 and EMU_BMODE to 0xD01 via the debugger

// according to the Boot Mode Table above. Build/Load project,

// Reset the device, and Run example

// $End_Boot_Table

// DESCRIPTION:

// This example tests all of the basic read/write MtoC IPC Driver functions

// available in F28M35x_Ipc.c

// The C28 project responds to the commands sent from the M3 project.

// Note that IPC INT1 and IPC INT2 are used for this example to process

// IPC commands.

// Watch Variables:

// ErrorFlag - Indicates an unrecognized command was sent from M3 to C28.

//###########################################################################

// $TI Release: F28M35x Support Library v208 $

// $Release Date: Tue Sep 6 09:31:30 CDT 2016 $

// $Copyright: Copyright (C) 2011-2016 Texas Instruments Incorporated -

// http://www.ti.com/ ALL RIGHTS RESERVED $

//###########################################################################

#include "DSP28x_Project.h" // Device Headerfile and Examples Include File

#include "F28M35x_Ipc_drivers.h"

//*****************************************************************************

// Definitions used in this example

//*****************************************************************************

#define C28_CTOM_PASSMSG 0x0003FBF4 // Used by C28 to pass address

// of local variables to perform

// actions on

#define M3_CTOM_PASSMSG 0x2007F7E8

#define M3_S0SARAM_START 0x20008000

//*****************************************************************************

// Function Prototypes

//*****************************************************************************

__interrupt void MtoCIPC1IntHandler(void);

__interrupt void MtoCIPC2IntHandler(void);

void FunctionCall(void);

void FunctionCallParam(Uint32 ulParam);

void Error (void);

//*****************************************************************************

// At least 1 volatile global tIpcController instance is required when using

// IPC API Drivers.

//*****************************************************************************

volatile tIpcController g_sIpcController1;

volatile tIpcController g_sIpcController2;

//*****************************************************************************

// Global variable used in this example to track errors

//*****************************************************************************

volatile Uint16 ErrorFlag;

volatile Uint32 FnCallStatus;

//*****************************************************************************

// Global variables used in this example to read/write data passed between

// M3 and C28

//*****************************************************************************

Uint16 usWWord16;

Uint32 ulWWord32;

Uint16 usMBuffer[256];

//*****************************************************************************

// Main Function

//*****************************************************************************

void

main(void)

{

// Define Local Variables

Uint32 *pulMsgRam;

Uint16 counter;

unsigned short *pusMBufferPt;

unsigned short usMBuffer[128] = {741, 974, 2345, 764, 331, 456, 321, 989};

// Step 1. Initialize System Control (Performed by M3):

// PLL, WatchDog, enable Peripheral Clocks

// InitSysCtrl();

// Step 2. Initialize GPIO:

// InitGpio(); // Skipped for this example

// Step 3. Clear all interrupts and initialize PIE vector table:

// Disable CPU interrupts

DINT;

// Initialize PIE control registers to their default state.

// The default state is all PIE interrupts disabled and flags

// are cleared.

// This function is found in the F28M35x_PieCtrl.c file.

InitPieCtrl();

// Disable CPU interrupts and clear all CPU interrupt flags:

IER = 0x0000;

IFR = 0x0000;

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

// This will populate the entire table, even if the interrupt

// is not used in this example. This is useful for debug purposes.

// The shell ISR routines are found in F28M35x_DefaultIsr.c.

// This function is found in F28M35x_PieVect.c.

InitPieVectTable();

// Interrupts that are used in this example are re-mapped to

// ISR functions found within this file.

EALLOW; // This is needed to write to EALLOW protected registers

PieVectTable.MTOCIPC_INT1 = &MtoCIPC1IntHandler;

PieVectTable.MTOCIPC_INT2 = &MtoCIPC2IntHandler;

EDIS; // This is needed to disable write to EALLOW protected registers

// Step 4. Initialize the Device Peripherals:

IPCCInitialize (&g_sIpcController1, IPC_INT1, IPC_INT1);

IPCCInitialize (&g_sIpcController2, IPC_INT2, IPC_INT2);

// Step 5. User specific code, enable interrupts:

// Enable CPU INT1 which is connected to MTOCIPC INT1-4:

IER |= M_INT11;

// Enable MTOCIPC INTn in the PIE: Group 11 interrupts

PieCtrlRegs.PIEIER11.bit.INTx1 = 1; // MTOCIPC INT1

PieCtrlRegs.PIEIER11.bit.INTx2 = 1; // MTOCIPC INT2

// Enable global Interrupts and higher priority real-time debug events:

EINT; // Enable Global interrupt INTM

ERTM; // Enable Global realtime interrupt DBGM

// Initialize all variables.

ErrorFlag = 0;

FnCallStatus = 0;

usWWord16 = 0;

ulWWord32 = 0;

for (counter = 0; counter < 256; counter++)

{

usMBuffer[counter] = 0;

}

// Point array to address in CTOM MSGRAM for passing variable locations

pulMsgRam = (void *)M3_CTOM_PASSMSG;//C28_CTOM_PASSMSG;

pusMBufferPt = (void *)M3_S0SARAM_START;

// Write addresses of variables where words should be written to pulMsgRam

// array.

// 0 = Address of 16-bit word to write to.

// 1 = Address of 32-bit word to write to.

// 2 = Address of buffer to block write to.

// 3 = Address of FunctionCall() function to call.

// 4 = Address of FunctionCallParam() function to call.

// 5 = Address of 32-bit FnCallStatus variable to check function call

// executed

pulMsgRam[0] = (unsigned long)&usWWord16;

pulMsgRam[1] = (unsigned long)&ulWWord32;

pulMsgRam[2] = (unsigned long)&usMBuffer[0];

pulMsgRam[3] = (unsigned long)&FunctionCall;

pulMsgRam[4] = (unsigned long)&FunctionCallParam;

pulMsgRam[5] = (unsigned long)&FnCallStatus;

// Flag to M3 that the variables are ready in MSG RAM with CTOM IPC Flag 17

CtoMIpcRegs.CTOMIPCSET.bit.IPC17 = 1;

// Request Memory Access to S0 SARAM for C28 (Invokes

// IPCCtoMSetBits_Protected() function)

IPCCtoMReqMemAccess (&g_sIpcController2, S0_ACCESS, IPC_SX_C28MASTER,

ENABLE_BLOCKING);

while ((RAMRegs.CSxMSEL.all & S0_ACCESS) != S0_ACCESS)

{

}

// Write a block of data from C28 to S0 shared RAM which is then written to

// an M3 address.

for (counter = 0; counter < 256; counter++)

{

pusCBufferPt[counter] = usCBuffer[counter];

}

IPCCtoMBlockWrite(&g_sIpcController2, pulMsgRam,

(Uint32)pusMBufferPt, 128, IPC_LENGTH_16_BITS,

ENABLE_BLOCKING);

for(;;)

{

// Flag an Error if an Invalid Command has been received.

//

if (ErrorFlag == 1)

{

Error();

}

}

}

//*****************************************************************************

// Function run by IPC_FUNC_CALL command

//*****************************************************************************

void

FunctionCall (void)

{

FnCallStatus = 1;

}

void

FunctionCallParam (unsigned long ulParam)

{

FnCallStatus = ulParam;

}

//*****************************************************************************

// Function to Indicate an Error has Occurred (Invalid Command Received).

//*****************************************************************************

void

Error(void)

{

// An error has occurred (invalid command received). Loop forever.

for (;;)

{

}

}

//*****************************************************************************

// MtoC INT1 Interrupt Handler - Handles Data Word Reads/Writes

//*****************************************************************************

__interrupt void

MtoCIPC1IntHandler (void)

{

tIpcMessage sMessage;

// Continue processing messages as long as MtoC GetBuffer1 is full

while (IpcGet (&g_sIpcController1, &sMessage,

DISABLE_BLOCKING)!= STATUS_FAIL)

{

switch (sMessage.ulcommand)

{

case IPC_SET_BITS:

IPCMtoCSetBits(&sMessage);

break;

case IPC_CLEAR_BITS:

IPCMtoCClearBits(&sMessage);

break;

case IPC_DATA_WRITE:

IPCMtoCDataWrite(&sMessage);

break;

case IPC_DATA_READ:

IPCMtoCDataRead(&g_sIpcController1, &sMessage, ENABLE_BLOCKING);

break;

case IPC_FUNC_CALL:

IPCMtoCFunctionCall(&sMessage);

break;

default:

ErrorFlag = 1;

break;

}

}

// Acknowledge IPC INT1 Flag and PIE to receive more interrupts from group

// 11

CtoMIpcRegs.MTOCIPCACK.bit.IPC1 = 1;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP11;

}

//*****************************************************************************

// MtoC INT2 Interrupt Handler - Handles Data Block Reads/Writes

//*****************************************************************************

__interrupt void

MtoCIPC2IntHandler (void)

{

tIpcMessage sMessage;

// Continue processing messages as long as MtoC GetBuffer2 is full

while (IpcGet (&g_sIpcController2, &sMessage,

DISABLE_BLOCKING)!= STATUS_FAIL)

{

switch (sMessage.ulcommand)

{

case IPC_BLOCK_WRITE:

IPCMtoCBlockWrite(&sMessage);

break;

case IPC_BLOCK_READ:

IPCMtoCBlockRead(&sMessage);

break;

default:

ErrorFlag = 1;

break;

}

}

// Acknowledge IPC INT2 Flag and PIE to receive more interrupts from group

// 11

CtoMIpcRegs.MTOCIPCACK.bit.IPC2 = 1;

PieCtrlRegs.PIEACK.all = PIEACK_GROUP11;

}

Please let me know if i have to be more specific with my question ! Any help is greatly appreciated.