I am working on implemented peak-current mode control. It's working well for the most part but I'm seeing an issue with low RAMPMAXREF values. I have cycle-by-cycle limiting with dead-time working using the analog comparators to trigger a Digital Compare event that then triggers a T1 event in the AQ block of the PWM.

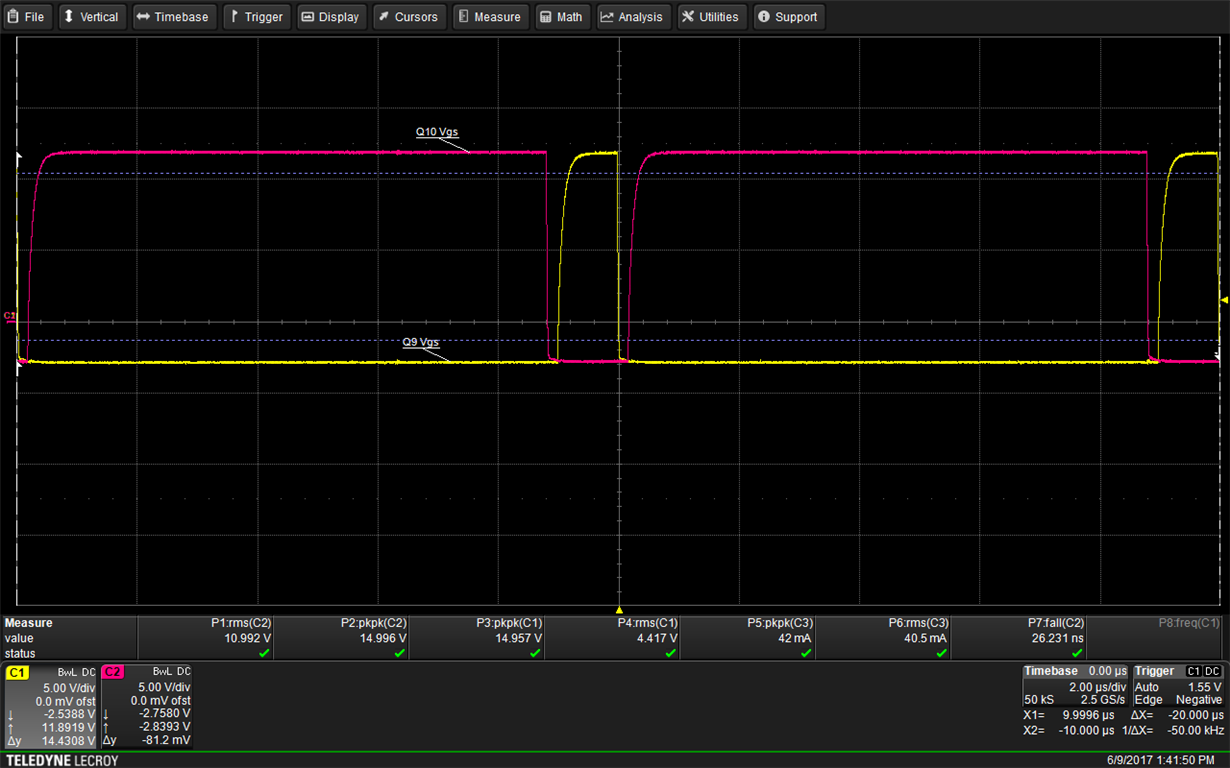

TBPRD = 999

CMPA = 500 (50% duty)

RAMPMAXREFS = 2000

Yellow = PWM A

Pink = PWM B

Expected behavior, PWM A channel is cut off before CMPA would normally trigger it.

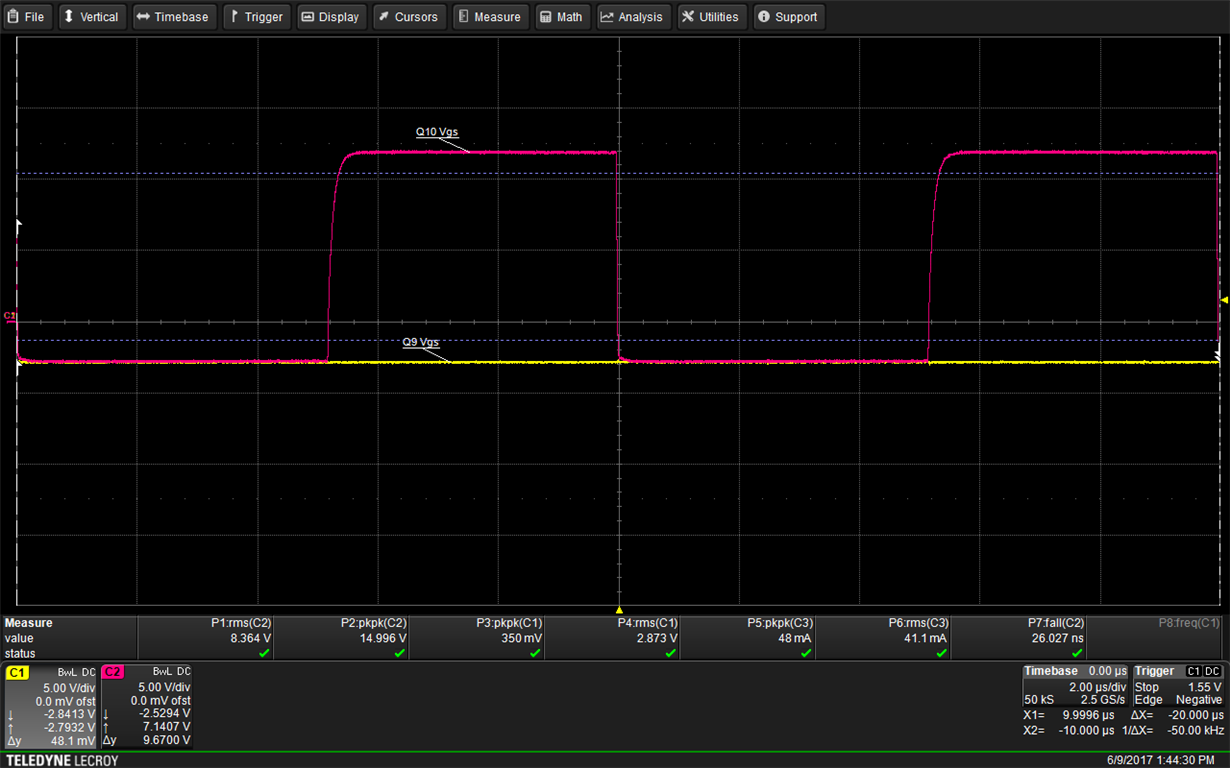

I'm having an issue when I set the RAMPMAXREFS to below a certain value, the gates behave unexpectedly.

RAMPMAXREFS = 0 (similar behavior up to around 450)

I would expect the analog comparator to trip instantly with a low RAMPMAXREFS and keep PWM A channel low and PWM B channel high. Instead I get this in-between behavior that looks like the comparator instantly trips for the PWM A channel but not the PWM B channel. Ocassionally the PWM B channel will stay low and the PWM A channel will output 50%. Certainly not a great situation.

Any ideas what is happening and how to resolve this? Any insight would be appreciated. Thank you!