Hi there,

I am using TMS320F28377D and I am looking for some clarifications, for correcting my understanding of the EPWM clock. It would be great if you could help.

In my software I have set:

ClkCfgRegs.PERCLKDIVSEL.bit.EPWMCLKDIV = 0; EPwm6Regs.TBCTL.bit.CLKDIV = 0; EPwm6Regs.TBCTL.bit.HSPCLKDIV = 0;

so according to SPRUM8C, Fig. 13-5 pag. 1478

my ePWM TBCLK should be the system clock, i.e. TBCLK = 1/200MHZ = 5 x 10^-9 =5ns.

I am using EPWM6 in UP-DOWN mode, and I have setup

EPwm6Regs.TBPRD = 500;

so the PWM period is TPWM = 2 * TBPRD * TBCLK = 5 x 10^-6 = 5us (SPRUHM8C, pag. 1480), i.e. I am switching the converter at 200kHz, and I can see this from my actual setup. I assume that this means that my calculations above are correct.

The questions are:

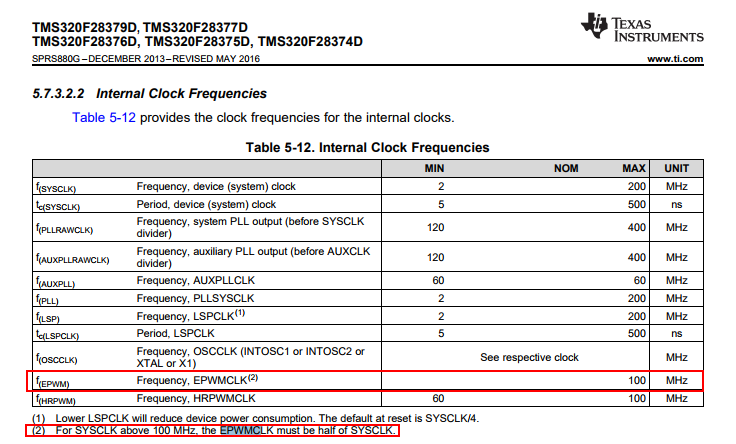

(1) Is there any limit on the TBLCK, i.e. am I using a TBCLK too low? (is there a 100MHz limit?)

(2) Also, I have noticed that:

ClkCfgRegs.SYSCLKDIVSEL.bit.PLLSYSCLKDIV = 1

is this influencing my calculation above? Is the system clock still 200MHz? even with the above set PLLSYSCLKDIV = 1?

Thank you for your kind help,

Leo