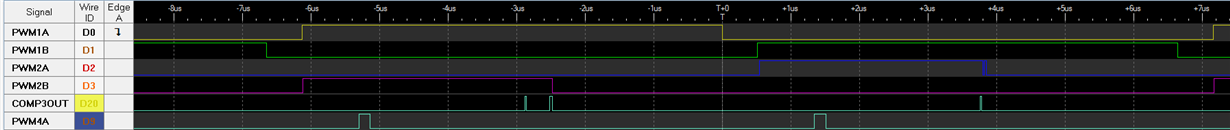

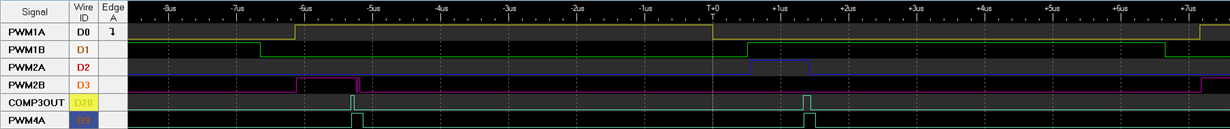

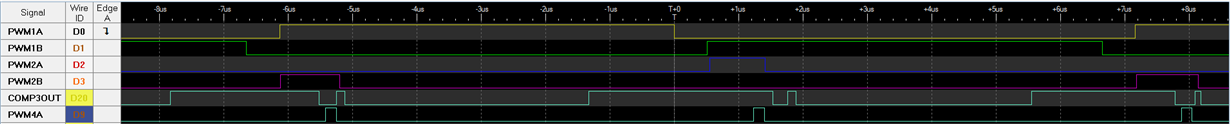

Hi, I'm working on a peak current control application using internal blanking window and ramp generator hardware blocks in the F28035. While configuring the ramp generator I ran into some problems. A current spike at the beginning of the period is blanked out with blanking window so it won't cause tripping, but it will trigger the comparator and cause the ramp generator to reset to its starting value for the rest of the period. The actual current ramp won't trigger the comparator again until current reaches RAMPMAXVREF level causing a wider pulse and possibly some fast width changes. How is the ramp generator intended to be used with the blanking window enabled?

Best regards

Pauli