Hi champs,

My customer has below questions of CAN module,

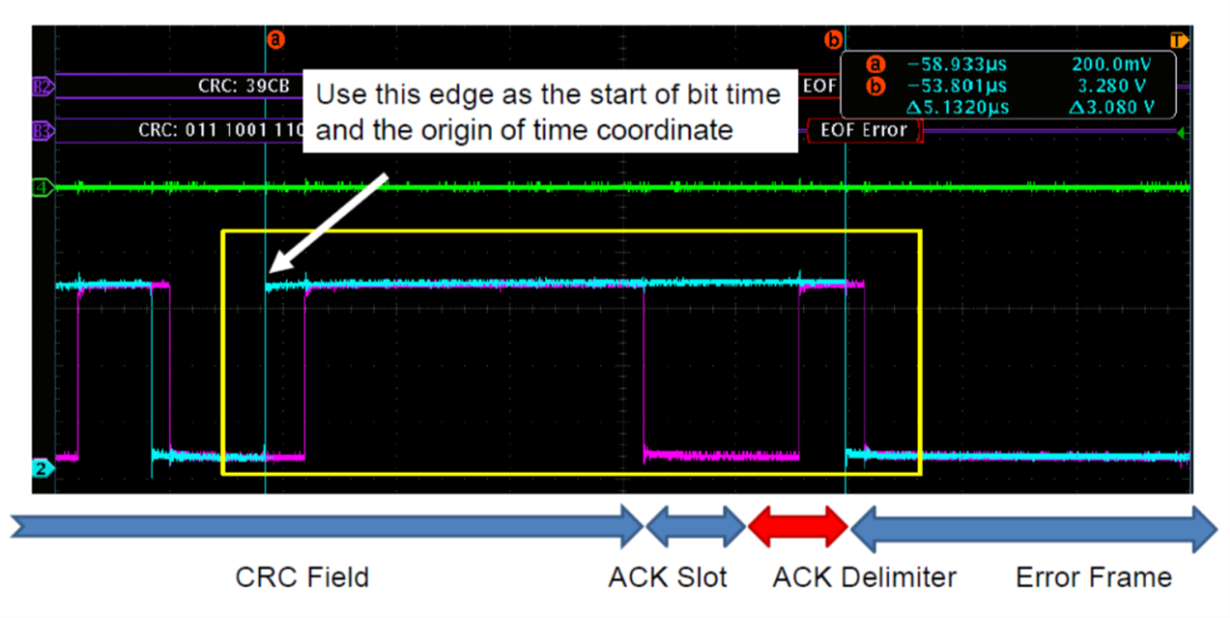

- Is it possible to get detailed data packet content information when CAN module is facing bit error problem?

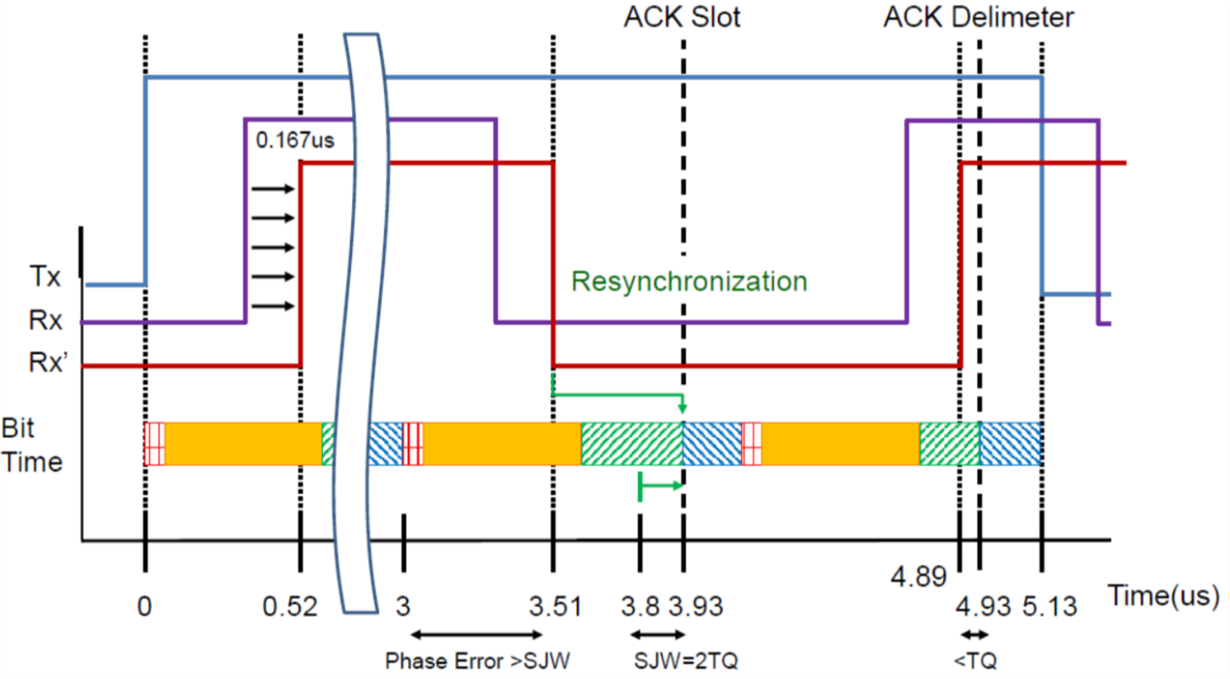

- When sample point is behind edge and the timer interval is less than 1 Time Quantum, will this sample timing cause a bit error?

Please advise your idea if any, thanks for help.

Regards,

Luke