I am using EMIF in 16-bit async mode. Per the technical manual, A0 is connected to EM1BA1, A1 to EM1A0, and so on. The EMIF1 is configured as follows:

EALLOW();

m_psCpuSysRegs->PCLKCR1.bit.EMIF1 = 1u;

s_reg_EMIF1CONFIG->EMIF1ACCPROT0.all = 0x0u;

s_reg_EMIF1CONFIG->EMIF1MSEL.all = 0x93A5CE71UL;

s_reg_EMIF1CONFIG->EMIF1ACCPROT0.all = 0x0u;

s_reg_EMIF1CONFIG->EMIF1COMMIT.all = 0x1u;

s_reg_EMIF1CONFIG->EMIF1LOCK.all = 0x1u;

EDIS();

setup_emif1_pinmux_async_16bit(0u);

s_reg_EMIF1->ASYNC_CS2_CR.all =

(EMIF_ASYNC_ASIZE_16 |

EMIF_ASYNC_TA_3 |

EMIF_ASYNC_RHOLD_4 |

EMIF_ASYNC_RSTROBE_4 |

EMIF_ASYNC_RSETUP_4 |

EMIF_ASYNC_WHOLD_4 |

EMIF_ASYNC_WSTROBE_4 |

EMIF_ASYNC_WSETUP_4 |

EMIF_ASYNC_EW_DISABLE |

EMIF_ASYNC_SS_DISABLE );

m_pu16FPGA_Adr = (uint16_t *)EMIF1_CS2_START_ADDR;

for(i=0u;i<8u;i++)

{

*m_pu16FPGA_Adr++ = m_au16FPGA_Output[i];

}

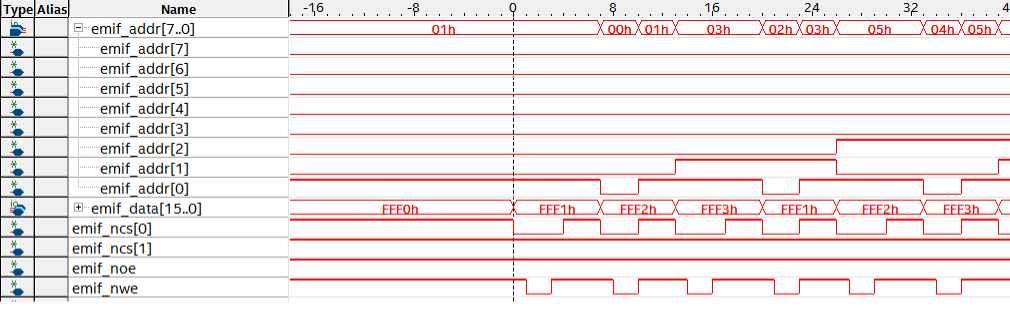

Please see the attached file for EMIF bus signals. The address bus signals are expanded. The EM1BA1 bus line (least significant address line in 16-bit mode), toggles in reverse. See the bit patter for 3 least significant bits:

Address written Address on Bus

000 001

001 000

010 011

011 010 etc.

Also, only EM1BA1 reverts to logic high when CS becomes inactive. All other address bus lines stay in their previous states.

Thanks for your help.

Zubair Hameed