Hi all! ;)

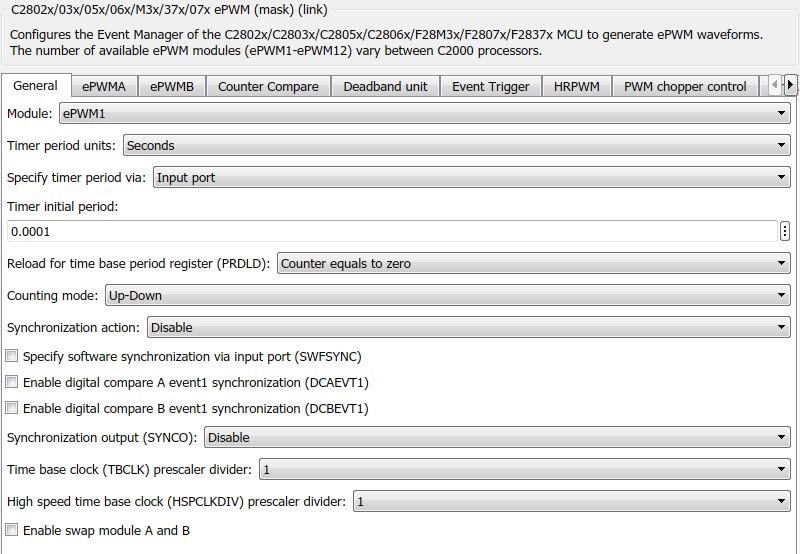

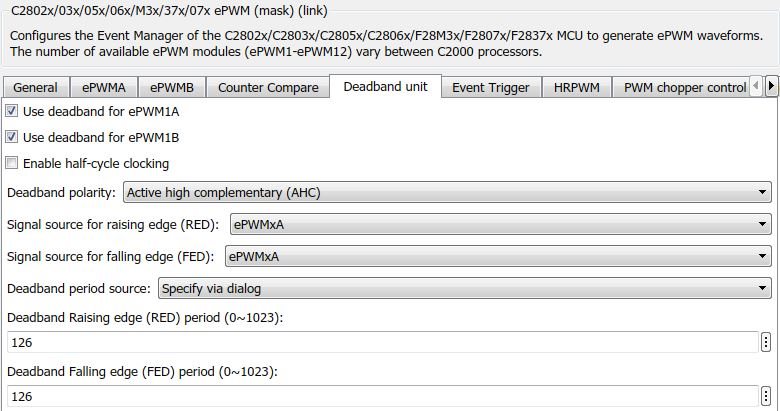

I have now finished the hardware work to build my own three-phase inverter for motor control. The inverter shall be run by my F28069M-LaunchPad. To avoid a shoot-through in the IGBT-module (B6 bridge topology) I wanted to insert a dead time between the falling edge and the next rising edge. I wanted the dead time to be 1.4 µs which is about 126 clock cycles on my 90 MHz MCU.

I found post here on the E2E forums that describes all the necessary steps to set such a dead time in the "Deadband unit" tab in Simulink:

https://e2e.ti.com/support/microcontrollers/c2000/f/171/p/152067/551099#551099

However, I set everything just like mentioned in this post but my oscilloscope shows that there is no deadband inserted between the falling edge of one switch and the rising edge of the other switch. Or let's better put it this way: The deadband of 1.4 µs is indeed inserted, but not only the rising edge is delayed, also the falling edge is delayed. (I found this out because at 10 % duty cycle the ePWM1A signal is constantly low and the ePWM1B signal is constantly high.) This should not happen. The falling edge should occur immediately and only the rising edge should be delayed.

Do you know what I did wrong here? I will attach some screenshots of my configuration below.

Best regards,

Armin