Other Parts Discussed in Thread: TPS3825

Hello everybody ,

I m on a F28069 @ 90MHz , ext quartz 20 MHz . I have already some thousands of units produced in the field , where I found some issues when a Reset by Watchdog is fired : many times uC does not restart and I can see a Train of pulse on the reset pin ( up to some tens ) before it starts back .

We understood HW on reset pin is not 100% correct ( we have reset pin with a 10nF to GND and straight connected to an external supervisor TPS3825 , no pullup ) and we ll fix for future production , but as for now we have units in the field and we need to understand and confirm what is happening now .

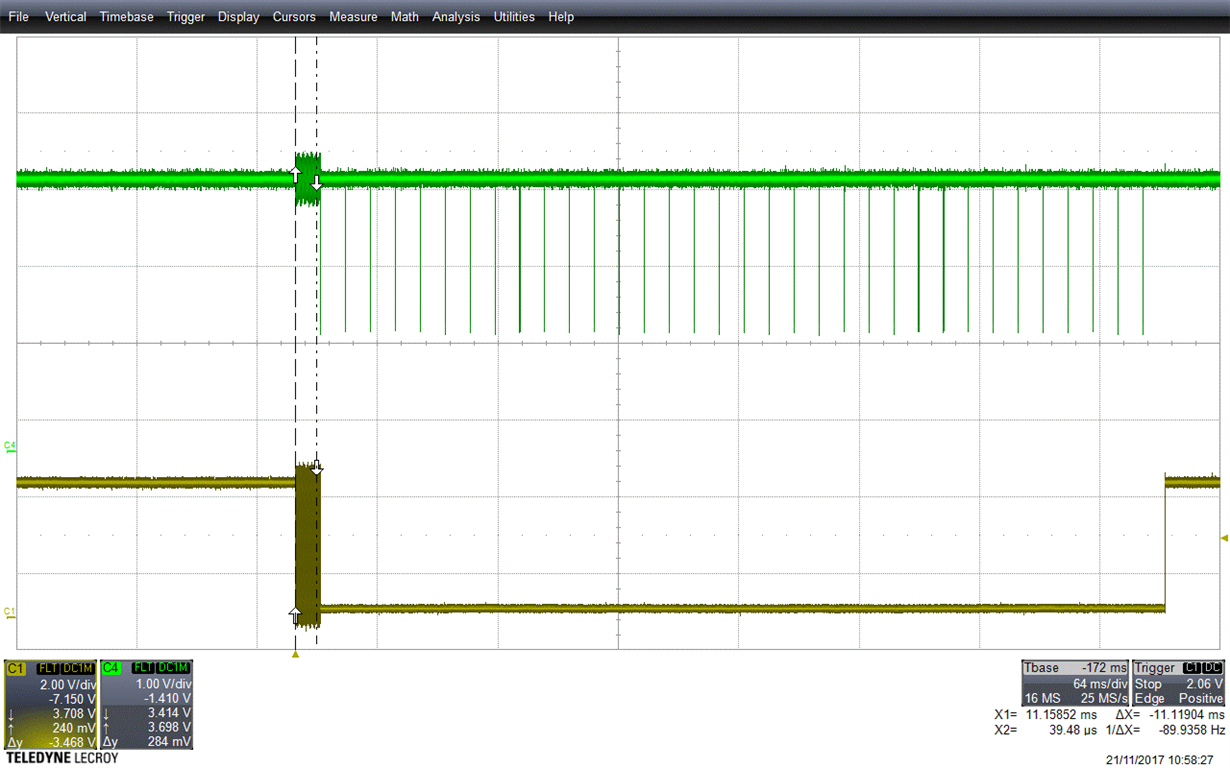

so as for now on the board I can see reset pin going down to about 1.62V , mS large of pulse is far more than the 512 clock cycle needed , but as said I see a train of reset pulse before the uC starts back ( in attach a scope image Green – XRS togglingYellow – HIGH a the beginning of main, TOGGLING during while(1) for watchdog reset) )

so questions:

1- why uC is not restarting ? Is it due to reset voltage level ?

2- what about PWMs statuw when CPU does not restart ? I can see them at low level stuck , but this is due or by chance ? I need them to stay grounded in this situation when CPU not executing

3- if I push watchdog to 500mS , then I only need 3-4 reset before CPU restarts executing ( instead of a very long train o pulse ) : why ?

any suggestion on what should I do ?

thank you very much

regards

Carlo