Part Number: TMS320F28377S

Hi,

I'm testing ePWM ISR using epwm_up_aq_cpu01 example.

I added GpioDataRegs.GPATOGGLE.bit.GPIO1 = 1; in the first line of the epwm1_isr to check interrupt latency.

because TRM says "The minimum interrupt latency is 14 SYSCLK cycles" so I expected 70ns+ latency.

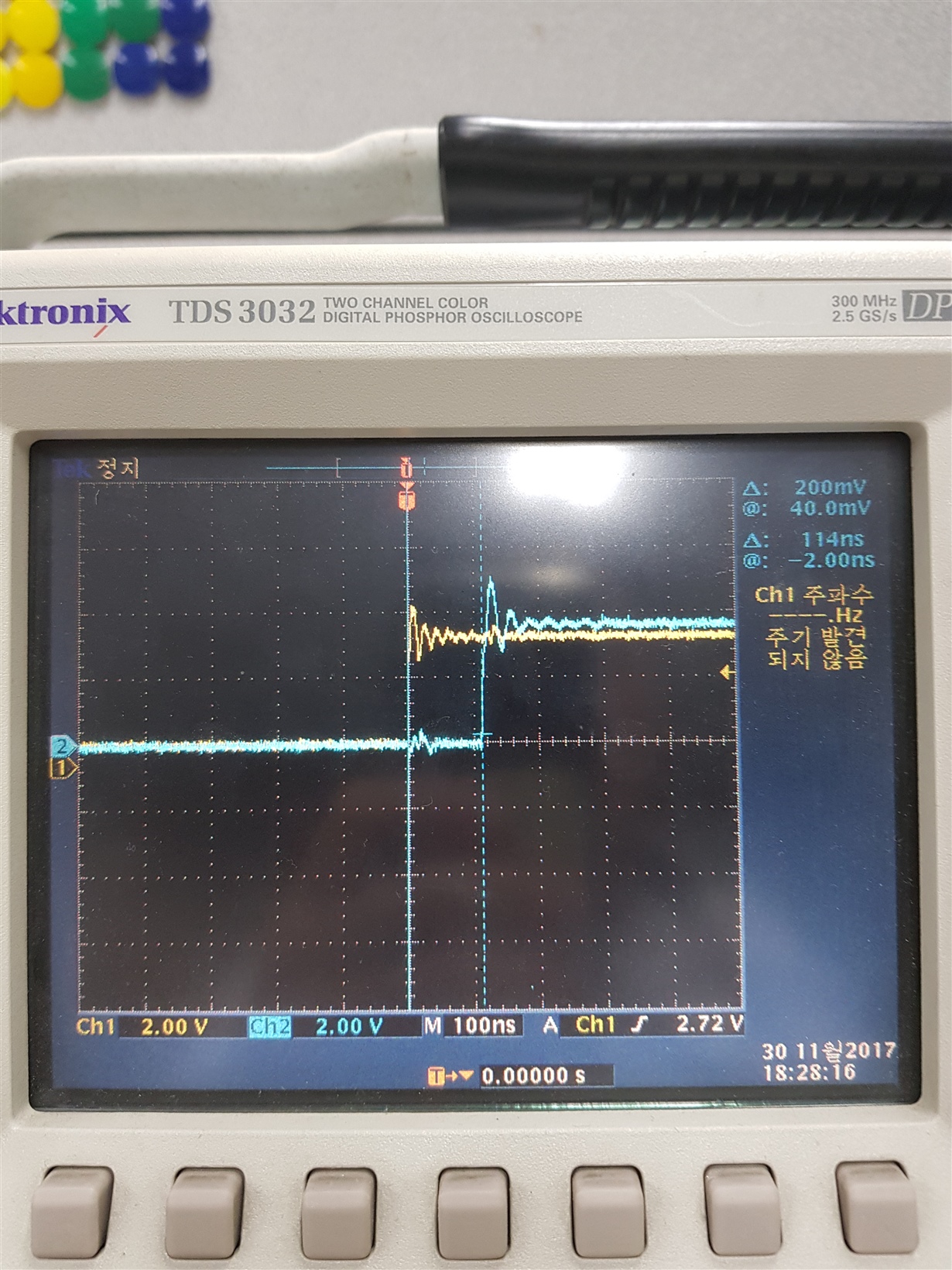

When I test with default clock prescaling setting as below, it shows 110ns which is very reasonable.

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV2; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV2;

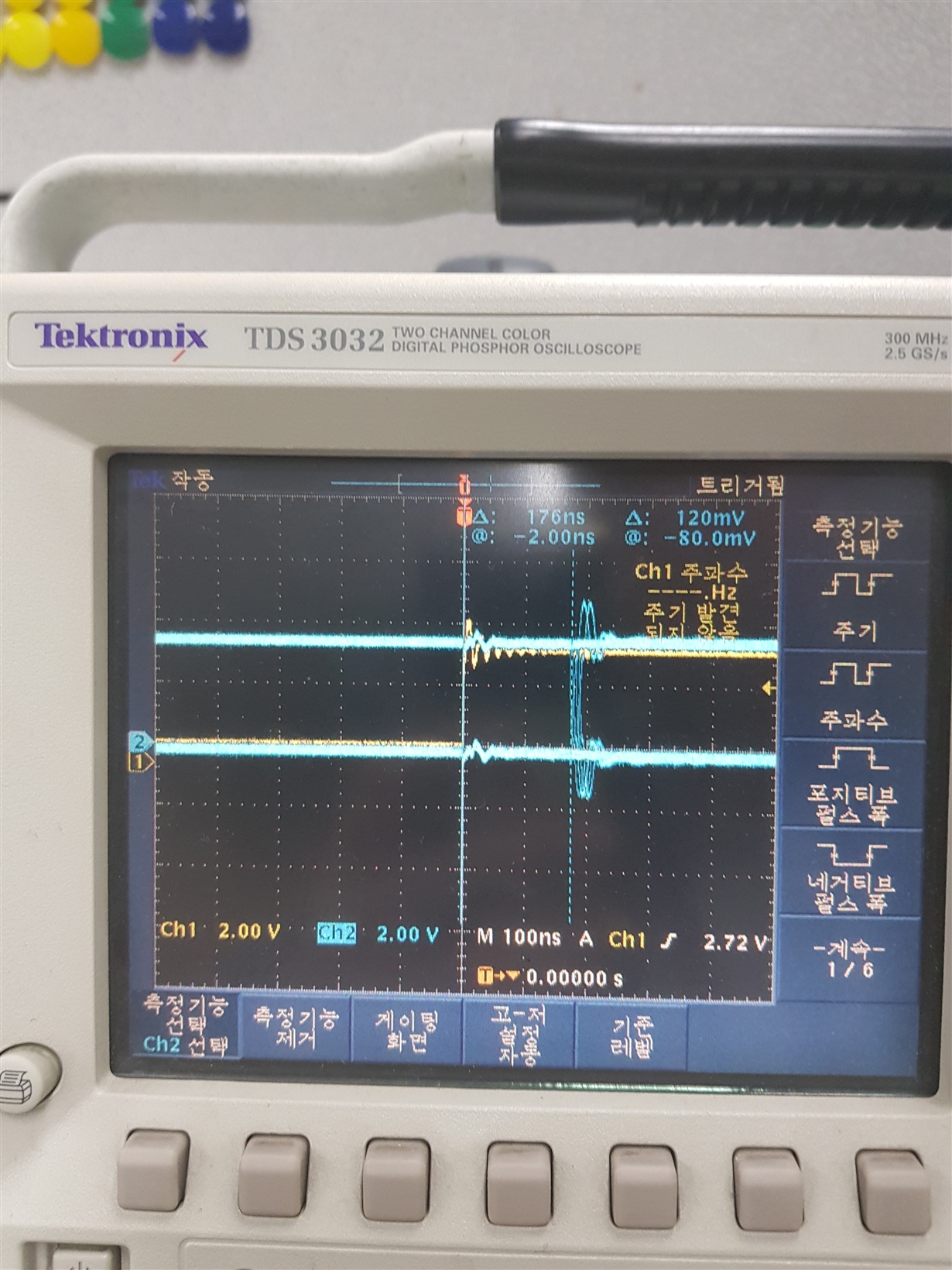

But when I changed clock prescaling value as below, interrupt latency is increased to 176ns.

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; // Clock ratio to SYSCLKOUT

EPwm1Regs.TBCTL.bit.CLKDIV = TB_DIV1;

Why is this happen?

I measured rising edge of the PWM and GPIO toggle time.

Regards,

Ted