We have a SCID driver that works properly when it runs on CPU1 (i.e. it transmits data), but when it has to work on CPU2 it does not works.

To move the SCID driver to CPU2 we have performed the following steps:

On CPU1

- Configuration of MUX for SCID

- Configuration of DevConfRegs in order to put CPU2 master for SCID

- Configuration of GPIOCtrlRegs.GPCSEl4.BIT.GPIO93 =0x2

- Configuration of GPIOCtrlRegs.GPCSEl4.BIT.GPIO94 =0x2

On CPU2

- Initialization of PIE Vector

- Configured CpuSysRegs in order to put CPU2 master for SCID

- Complete SCID configuration (the same that works on CPU1, including setup of Tx & Rx ISRs)

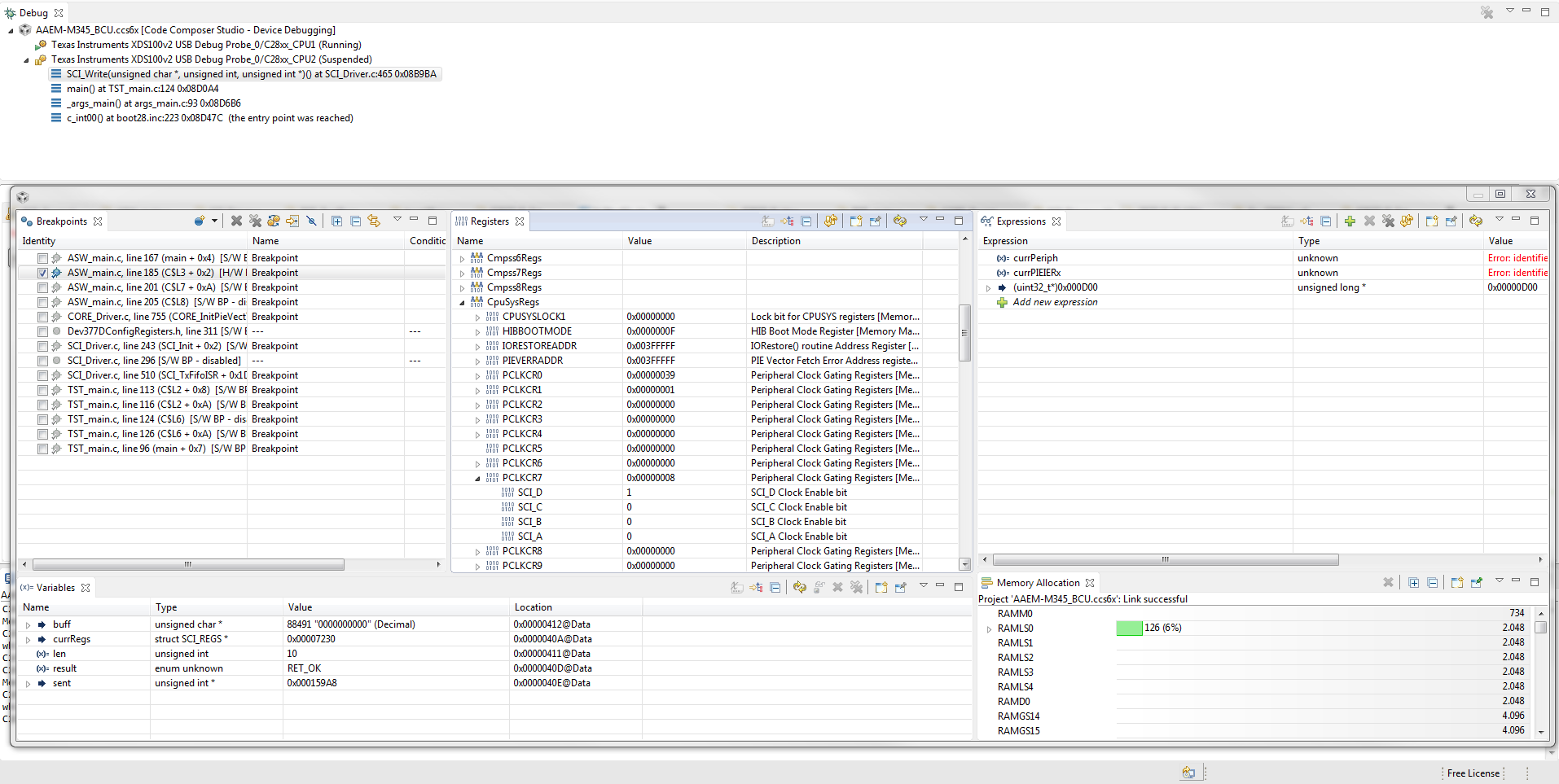

All registers work properly, but no Tx ISR trips.

I noticed that the PIE Vector table on CPU2 is not updated.

Where am I doing wrong?

By the way, is there a tutorial which deals with these issues, i.e. how a complete list of steps necessary to use peripherals on CPU2?

Thank you,

Nicola