Part Number: TMS320F28335

hi,

I'm doing a small experiment on DMA and ADC using example code. Example code name is Example_2833xAdcToDMA and this is converting ADC channel 0 to 4 in SEQ1 and transferring it to the DMA.

now i have changed the code little bit by changing ADC channel select from 8 to 4. Also i have done necessary changes in DMA configuration as follow,

InitAdc(); // For this example, init the ADC

// Specific ADC setup for this example:

AdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK;

AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS;

AdcRegs.ADCTRL1.bit.SEQ_CASC = 0; // 0 Non-Cascaded Mode

AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 0x1;

AdcRegs.ADCTRL2.bit.RST_SEQ1 = 0x1;

AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0;

AdcRegs.ADCCHSELSEQ1.bit.CONV01 = 0x1;

AdcRegs.ADCCHSELSEQ1.bit.CONV02 = 0x2;

AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3;

AdcRegs.ADCMAXCONV.bit.MAX_CONV1 = 3; // Set up ADC to perform 4 conversions for every SOC

//Step 5. User specific code, enable interrupts:

// Initialize DMA

DMAInitialize();

// Clear Table

for (i=0; i<BUF_SIZE; i++)

{

DMABuf1[i] = 0;

}

// Configure DMA Channel

DMADest = &DMABuf1[0]; //Point DMA destination to the beginning of the array

DMASource = &AdcMirror.ADCRESULT0; //Point DMA source to ADC result register base

DMACH1AddrConfig(DMADest,DMASource);

DMACH1BurstConfig(3,1,10);

DMACH1TransferConfig(9,0,0);

DMACH1WrapConfig(0,0,0,1);

DMACH1ModeConfig(DMA_SEQ1INT,PERINT_ENABLE,ONESHOT_DISABLE,CONT_DISABLE,SYNC_DISABLE,SYNC_SRC,

OVRFLOW_DISABLE,SIXTEEN_BIT,CHINT_END,CHINT_ENABLE);

StartDMACH1();

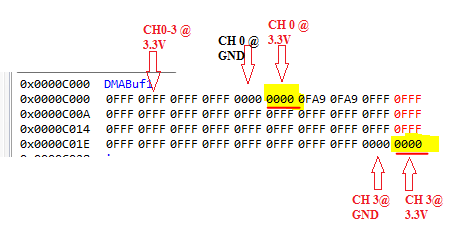

Remaining code and settings are same. the problem i'm facing here is ADC conversion placed properly at RAM on 1st trigger and on 2nd trigger its places previous ADC data. so ADC result placed at DMA RAM every alternate trigger . What could be the possible causes? is that possible to use ADC only for the first 4 conversion and on next trigger, conversion will start from the CH0?