I am debugging 28377D with CCS. In my application, I want to reset CPU1 and CPU2 separately. The F2837xD peripheral driver library offers a function named SysCtl_resetDevice() to perform a watchdog reset.

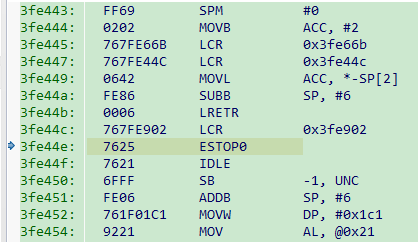

It works well for CPU1, that is after CPU1 watchdog reset, the PC of CPU1 will go to main() again. However, it works failed for CPU2. After watchdog reset of CPU2, the PC will go to 0x3fe44e which is a ESTOP0. At the meantime, CPU1 runs normally. Then I reset and restart CPU2 using CCS, the CPU2 can run again.

Question 1: what's the difference between CCS reset and watchdog reset for CPU2?

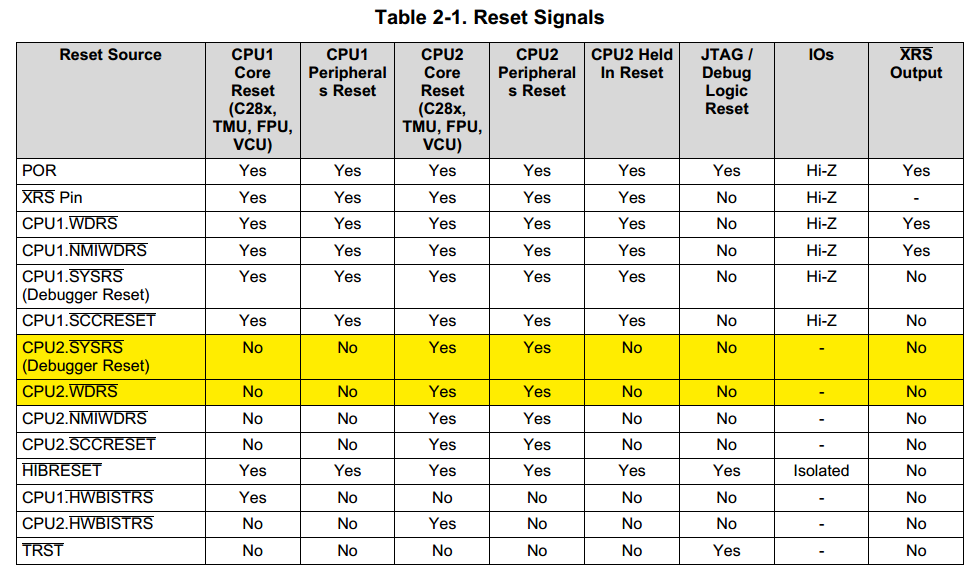

According to the TRM, the CCS reset and watchdog reset for CPU2 are the same shown below.

After watchdog reset of CPU2, why CPU2 doesn't go to main() again?

Question 2: what's the boot sequence for CPU2 in emulation mode?

In my project, the CPU1 doesn't send IPC command to boot CPU2. Does this mean that CPU2 can boot itself without CPU1's control in emulation mode?

When CPU2 enters wait boot mode, it keeps in reset and waits for the boot command from CPU1. Is this true for CPU2 in emulation mode?

Question 3: Is there any method for CPU1 to reset CPU2 without interrupting CPU1?