Part Number: F28M35H52C

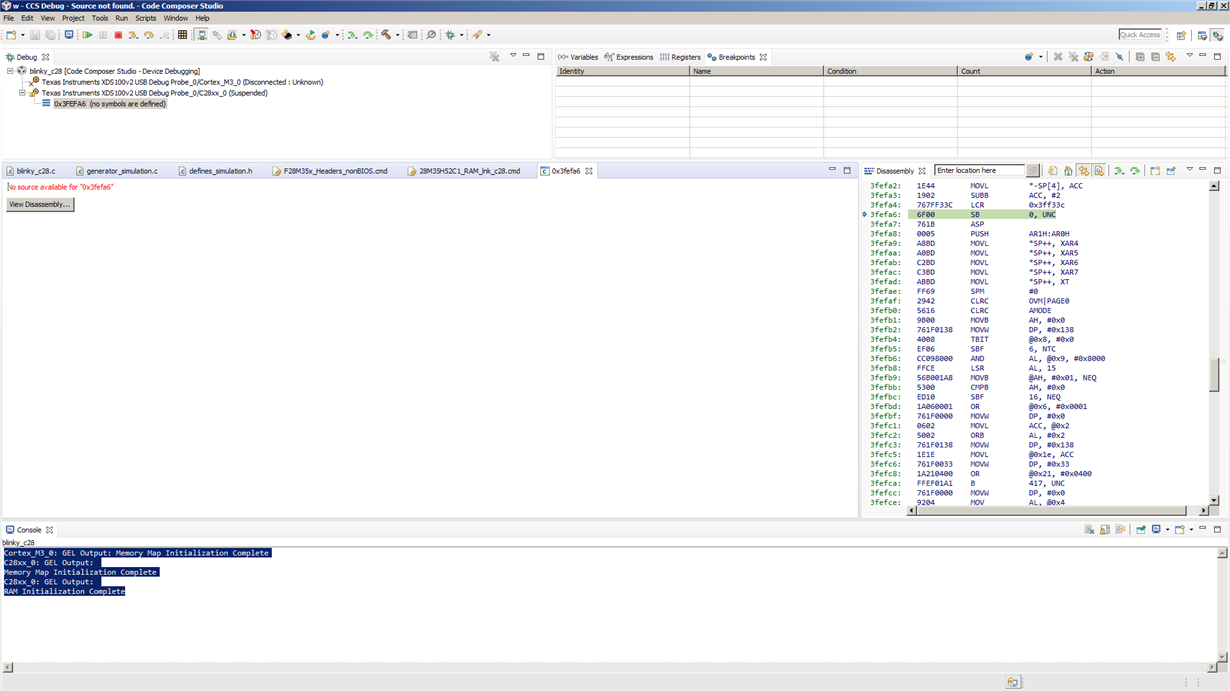

I am trying to load and run a program from RAM because of the time it takes working with FLASH. I started with the blinky project for the C28x and could make it work. Then I decided to try to load and run it from RAM and in order to do that, I changed the properties of the project. I modified the configuration and set RAM [ Active ] which changed the .cmd file used for linking. However, it does not allow me to start the execution of the program. Actually, when I click on the debug button, Code Composer seems to load the program but when it finishes, the device is already running (I can not start the execution on my own like in other cases) and when I suspend the execution, a window like the one shown appears:

I think I have problems with the boot mode but I saw the possible configurations of the switches and any of them allow me to boot de C28x from RAM.

I think I have problems with the boot mode but I saw the possible configurations of the switches and any of them allow me to boot de C28x from RAM.

Can anyone help me? Thanks in advance.