Other Parts Discussed in Thread: CONTROLSUITE, C2000WARE

Dear,

I have a full H-bridge to control. I use ePWM1 and ePWM2 for this.

ePWM1 is used for one branch and has phase shift zero.

epWM2 is used for other branch and the phase shift is variable to set the duty cycle.

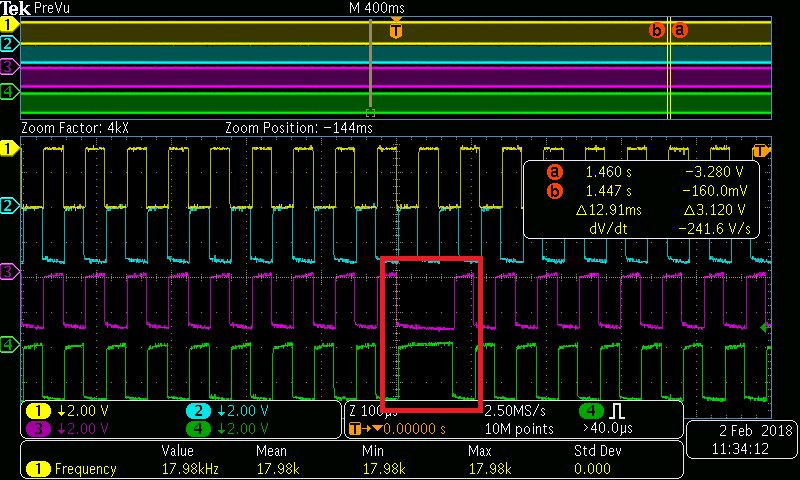

When I change the phase shift of ePWM2 the ePWM2 losses one cycle?

I change the phase shift by using EPwm2Regs.TBPHS.half.TBPHS.

Is there something I forgot to set-up?

This is the configuration I use:

// EPWM module 1

EPwm1Regs.AQCSFRC.bit.CSFA=ePWM_AQ_CLEAR;

EPwm1Regs.TBPRD=0;

EPwm1Regs.CMPA.half.CMPA=0;

EPwm1Regs.TBPHS.half.TBPHS=0;

EPwm1Regs.TBCTL.bit.CLKDIV=ePWM_DIV1;

EPwm1Regs.TBCTL.bit.HSPCLKDIV=ePWM_DIV1;

EPwm1Regs.TBCTL.bit.CTRMODE=ePWM_TB_COUNT_UP;

EPwm1Regs.TBCTL.bit.PHSEN=ePWM_TB_DISABLE;

EPwm1Regs.TBCTL.bit.PRDLD=ePWM_TB_SHADOW;

EPwm1Regs.TBCTL.bit.SYNCOSEL=ePWM_TB_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.SHDWAMODE=ePWM_CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE=ePWM_CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE=ePWM_CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE=ePWM_CC_CTR_ZERO;

EPwm1Regs.AQCTLA.bit.ZRO=ePWM_AQ_SET;

EPwm1Regs.AQCTLA.bit.CAU=ePWM_AQ_CLEAR;

EPwm1Regs.DBCTL.bit.OUT_MODE=ePWM_DB_ENABLE_FULL;

EPwm1Regs.DBCTL.bit.POLSEL=ePWM_DB_ACTIV_LOC;

EPwm1Regs.DBFED=50;

EPwm1Regs.DBRED=70;

// EPWM module 2

EPwm2Regs.AQCSFRC.bit.CSFA=ePWM_AQ_CLEAR;

EPwm2Regs.TBPRD=0;

EPwm2Regs.CMPA.half.CMPA=0;

EPwm2Regs.TBPHS.half.TBPHS=0;

EPwm2Regs.TBCTL.bit.CLKDIV=ePWM_DIV1;

EPwm2Regs.TBCTL.bit.HSPCLKDIV=ePWM_DIV1;

EPwm2Regs.TBCTL.bit.CTRMODE=ePWM_TB_COUNT_UP;

EPwm2Regs.TBCTL.bit.PHSEN=ePWM_TB_ENABLE;

EPwm2Regs.TBCTL.bit.PRDLD=ePWM_TB_SHADOW;

EPwm2Regs.TBCTL.bit.SYNCOSEL=ePWM_TB_SYNC_IN;

EPwm2Regs.CMPCTL.bit.SHDWAMODE=ePWM_CC_SHADOW;

EPwm2Regs.CMPCTL.bit.SHDWBMODE=ePWM_CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE=ePWM_CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE=ePWM_CC_CTR_ZERO;

EPwm2Regs.AQCTLA.bit.ZRO=ePWM_AQ_SET;

EPwm2Regs.AQCTLA.bit.CAU=ePWM_AQ_CLEAR;

EPwm2Regs.DBCTL.bit.OUT_MODE=ePWM_DB_ENABLE_FULL;

EPwm2Regs.DBCTL.bit.POLSEL=ePWM_DB_ACTIV_LOC;

EPwm2Regs.DBFED=30;

EPwm2Regs.DBRED=40;

//********************************************************

// Step 2: Configure ePWM trip zones

//********************************************************

// Enable CPU CLK fail

EPwm1Regs.TZSEL.bit.OSHT5=TRUE;

EPwm2Regs.TZSEL.bit.OSHT5=TRUE;

// Enable driver fault

EPwm1Regs.TZSEL.bit.OSHT1=TRUE;

EPwm2Regs.TZSEL.bit.OSHT2=TRUE;

// Configure driver fault to trip zone input

// Fault 1 is connected to GPIO14

TrigRegs.INPUT1SELECT=14;

// Fault 2 is connected to GPIO15

TrigRegs.INPUT2SELECT=15;

// Side A of bridge will be swithed off

EPwm1Regs.TZCTL.bit.TZA=ePWM_TZ_FORCE_LO;

EPwm2Regs.TZCTL.bit.TZA=ePWM_TZ_FORCE_LO;

Changing the parameters of the control is done like this:

period=11111;

EPwm1Regs.TBPRD=(uint16)period;

EPwm1Regs.CMPA.half.CMPA=(uint16)(period>>1);

EPwm2Regs.TBPRD=(uint16)period;

EPwm2Regs.CMPA.half.CMPA=(uint16)(period>>1);

// Set phase in clock pulses according ° setting

EPwm1Regs.TBPHS.half.TBPHS=0;

EPwm2Regs.TBPHS.half.TBPHS=(uint16)(period*(uint32)Phase/360);