Part Number: TMS320F28375D

Hi champs,

I have a question about EMIF2 16bit memory interface.

On TRM P.2612

-------------------------------------------------

The EMIF address pin EM1A[0] always provides the least significant bit of a 32-bit word address. Therefore, when interfacing to a 16-bit or 8-bit asynchronous device, the EM1BA[1] and EM1BA[0] pins provide the leastsignificant bits of the halfword or byte address, respectively.

-------------------------------------------------

This is for EMIF1.

When it uses EMIF2,

-------------------------------------------------

The EMIF address pin EM2A[0] always provides the least significant bit of a 32-bit word address. Therefore, when interfacing to a 16-bit or 8-bit asynchronous device, the EM2BA[1] and EM2BA[0] pins provide the leastsignificant bits of the halfword or byte address, respectively.

-------------------------------------------------

As above, is my understanding correct?

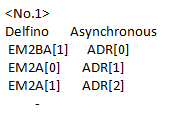

Does it work correctly when connected as follows?

Delfino Asynchronous

EM2A[0] ADR[0]

EM2A[1] ADR[1]

-

-

-

EM2A[12] ADR[12]

Regards,

Shinji Ueda