Other Parts Discussed in Thread: C2000WARE

Hi,

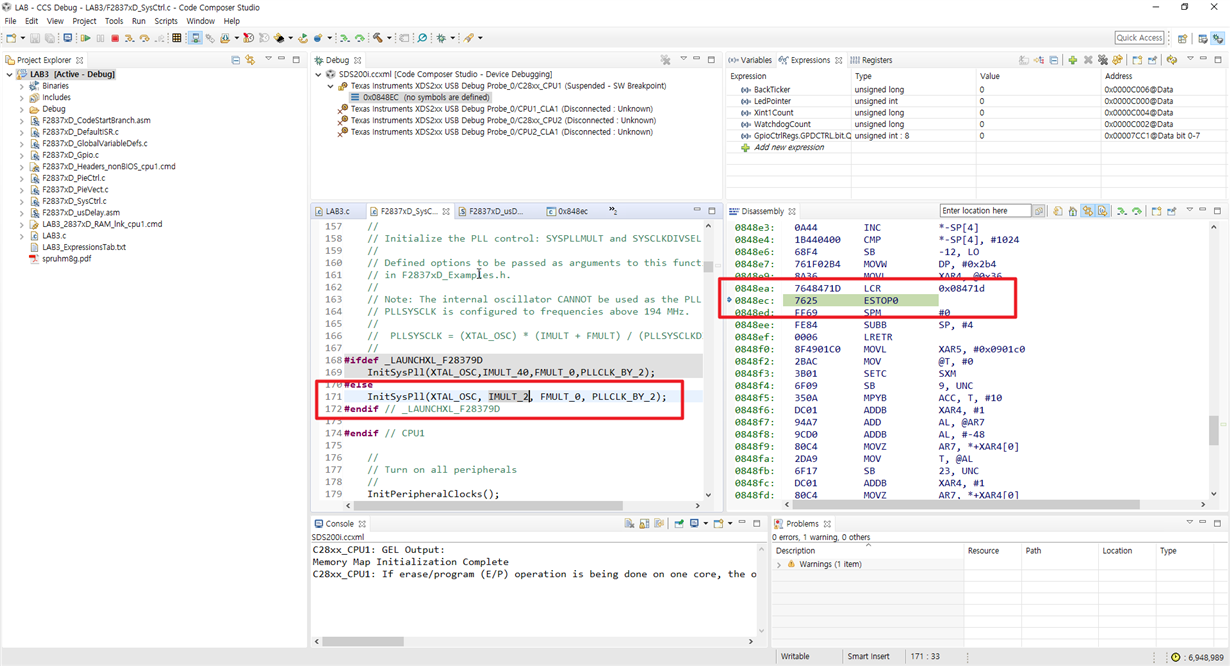

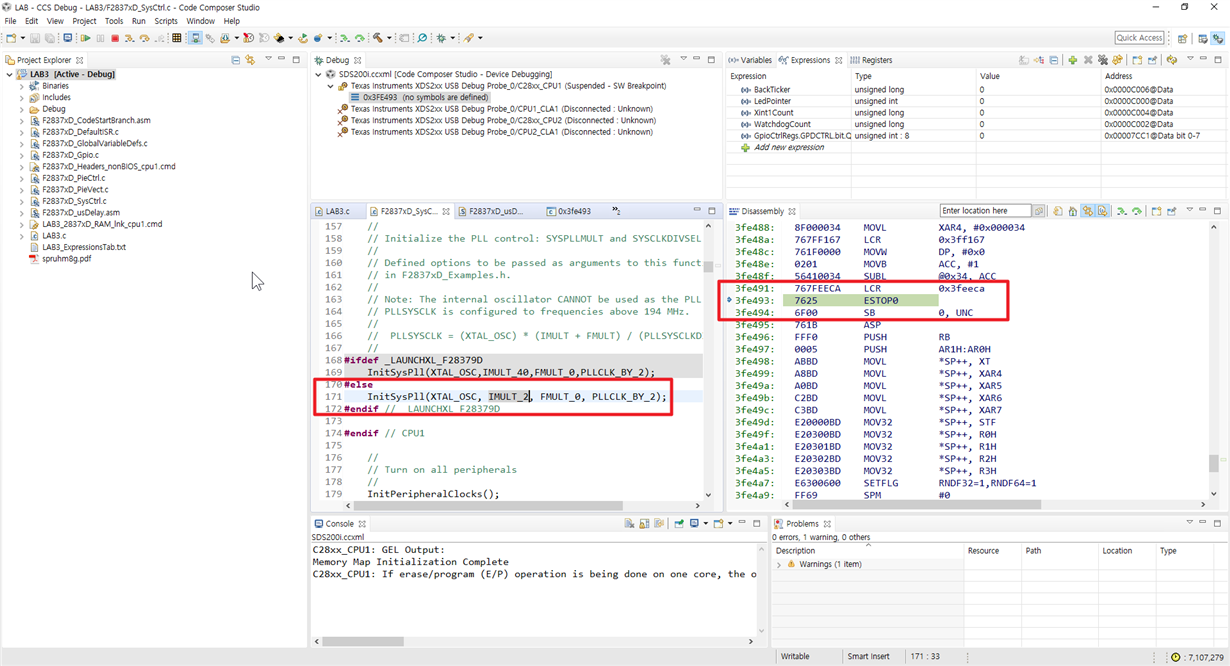

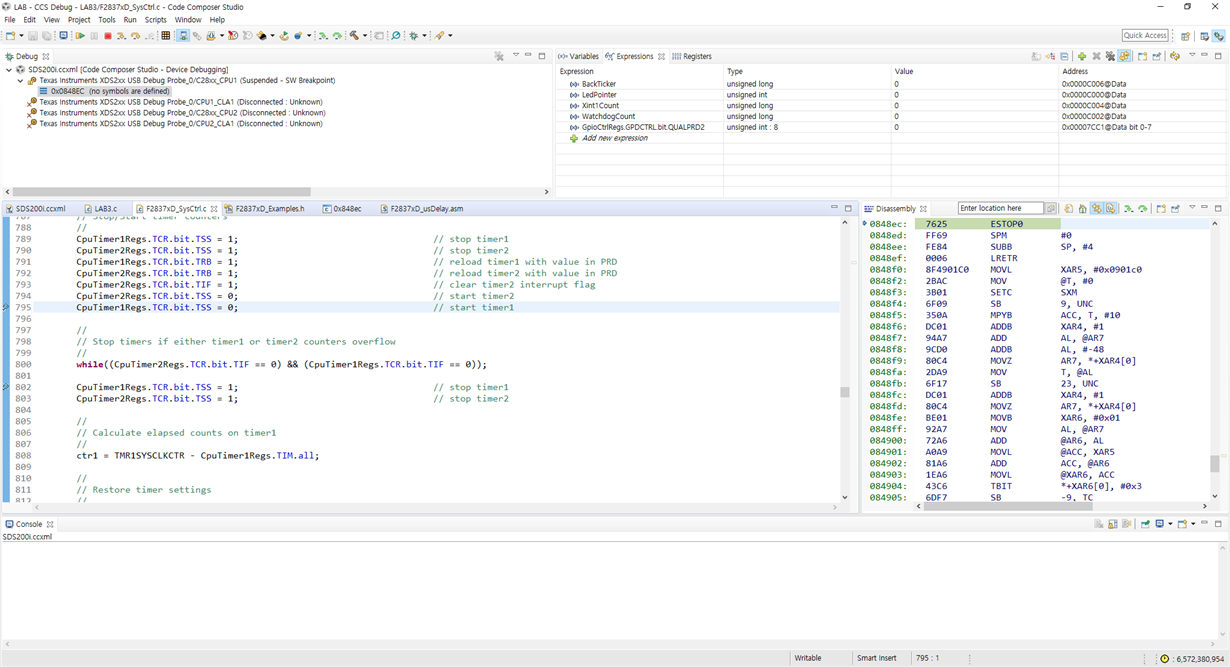

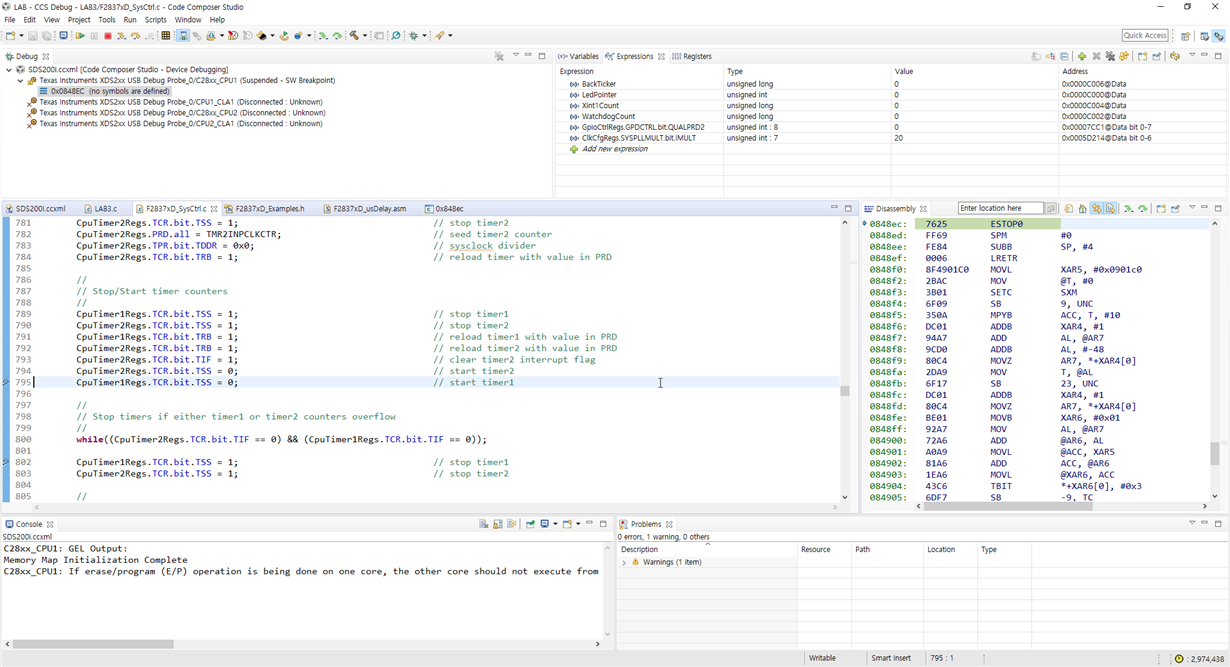

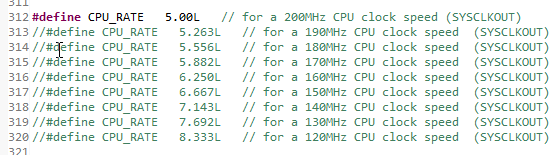

For testing the TMS320F28377D chip PLL circuit, I changed the argument of InitSysPll( ) function from IMULT_20 to IMULT_2 to lower the CPU clock frequency to 20MHz, and run it after rebuild the program.

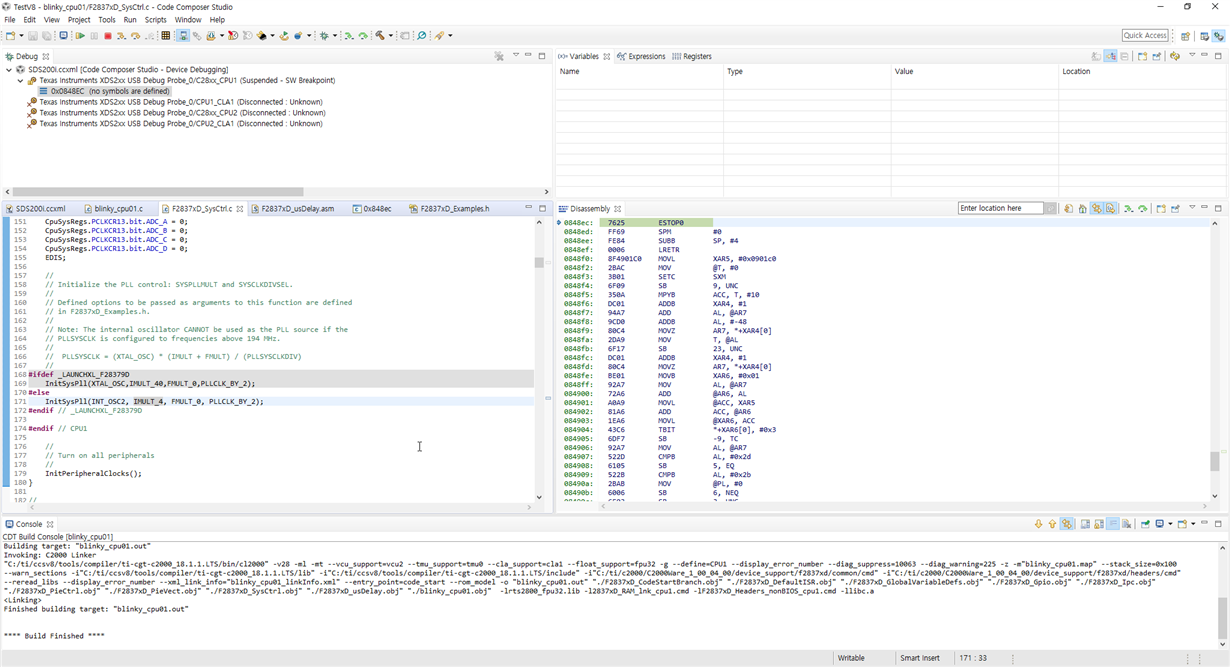

However, the main( ) function is not executed and PC halt in the ESTOP0 code at address 0x003FE493 as shown in the attached image.

Same problem occurs at other frequency settings, such as 10MHz & 5MHz, but does not cause problems at higher CPU clock frequencies, such as 100MHz.

I wonder if this problem is likely to be caused by the pull-up resistance and bypass capacitor value of the / XRS pin. (I currently use a 16kohm resistor and a 100nF capacitor.)

If it is caused by other causes, I want to know about it specifically.

Thanks in advance.