Part Number: TMS320F28335

Other Parts Discussed in Thread: C2000WARE, ADS7809

Hello,

I am using a 16bit ADC input to the McBSP-B, receive serial data MDRB on GPIO25, receive clock MCLKRB on GPIO60 and receive frame synch MFSRB on GPIO61.

My problem is the Receiver ready bit RRDY is not set and data in not loaded into Data Receive Register DRR1.

If the Transmit frame-synchronization polarity bit FSRP is toggled with the emulator at run time, I get good data in DRR1, it is like the receive frame-sync signal MFSRB is not starting a transfer.

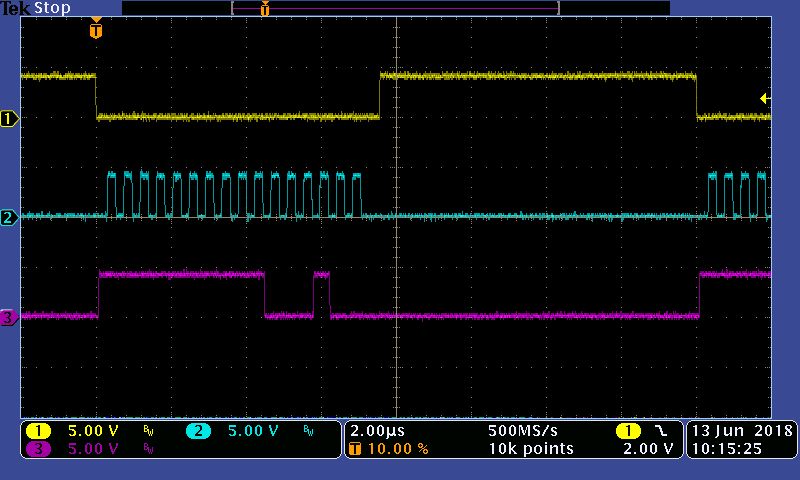

The oscope CH1 is MFSRB, CH2 is MCLKRB and CH3 is MDRB. When I read the GPIO inputs with the emulator all signals are correct.

void InitMcbspb(void)

{

// McBSP-B register settings

McbspbRegs.SPCR2.all=0x0000; // Reset FS generator, sample rate generator & transmitter

McbspbRegs.SPCR1.all=0x0000; // Reset Receiver, Right justify word

// McbspbRegs.SPCR1.bit.DLB = 1; // Enable loopback mode for test. Comment out for normal McBSP transfer mode.

McbspbRegs.MFFINT.all=0x0; // Disable all interrupts

McbspbRegs.RCR2.all=0x0; // Single-phase frame, 1 word/frame, No companding (Receive)

McbspbRegs.RCR1.all=0x0;

McbspbRegs.XCR2.all=0x0; // Single-phase frame, 1 word/frame, No companding (Transmit)

McbspbRegs.XCR1.all=0x0;

McbspbRegs.PCR.bit.FSXM = 1; // FSX generated internally, FSR derived from an external source

McbspbRegs.SRGR2.bit.CLKSM = 1; // CLKSM=1 (If SCLKME=0, i/p clock to SRG is LSPCLK)

McbspbRegs.SRGR2.bit.FPER = 31; // FPER = 32 CLKG periods

McbspbRegs.SRGR1.bit.FWID = 0; // Frame Width = 1 CLKG period

McbspbRegs.SRGR1.bit.CLKGDV = CLKGDV_VAL; // CLKG frequency = LSPCLK/(CLKGDV+1)

delay_loop(); // Wait at least 2 SRG clock cycles

InitMcbspb16bit(); // 16-bit word

McbspbRegs.PCR.bit.FSRP = 1; // Frame-synchronization pulse FSR is active low.

McbspbRegs.PCR.bit.CLKRP = 1; // Receive data sampled on rising edge of MCLKR

McbspbRegs.PCR.bit.CLKXM = 1; // CLKX generated internally, CLKR derived from an external source

delay_loop(); // Wait at least 2 SRG clock cycles

McbspbRegs.SPCR2.bit.GRST=1; // Enable the sample rate generator

clkg_delay_loop(); // Wait at least 2 CLKG cycles

McbspbRegs.SPCR2.bit.XRST=1; // Release TX from Reset

McbspbRegs.SPCR1.bit.RRST=1; // Release RX from Reset

McbspbRegs.SPCR2.bit.FRST=1; // Frame Sync Generator reset

}

void InitMcbspa16bit(void)

{

McbspaRegs.RCR1.bit.RWDLEN1=2; // 16-bit word

McbspaRegs.XCR1.bit.XWDLEN1=2; // 16-bit word

}

void InitMcbspbGpio(void)

{

EALLOW;

/* Configure McBSP-A pins using GPIO regs*/

// This specifies which of the possible GPIO pins will be McBSP functional pins.

// Comment out other unwanted lines.

//GpioCtrlRegs.GPAMUX1.bit.GPIO12 = 3; // GPIO12 is MDXB pin (Comment as needed)

// GpioCtrlRegs.GPAMUX2.bit.GPIO24 = 3; // GPIO24 is MDXB pin (Comment as needed)

//GpioCtrlRegs.GPAMUX1.bit.GPIO13 = 3; // GPIO13 is MDRB pin (Comment as needed)

GpioCtrlRegs.GPAMUX2.bit.GPIO25 = 3; // GPIO25 is MDRB pin (Comment as needed)

//GpioCtrlRegs.GPAMUX1.bit.GPIO14 = 3; // GPIO14 is MCLKXB pin (Comment as needed)

// GpioCtrlRegs.GPAMUX2.bit.GPIO26 = 3; // GPIO26 is MCLKXB pin (Comment as needed)

// GpioCtrlRegs.GPAMUX1.bit.GPIO3 = 3; // GPIO3 is MCLKRB pin (Comment as needed)

GpioCtrlRegs.GPBMUX2.bit.GPIO60 = 1; // GPIO60 is MCLKRB pin (Comment as needed)

//GpioCtrlRegs.GPAMUX1.bit.GPIO15 = 3; // GPIO15 is MFSXB pin (Comment as needed)

// GpioCtrlRegs.GPAMUX2.bit.GPIO27 = 3; // GPIO27 is MFSXB pin (Comment as needed)

// GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 3; // GPIO1 is MFSRB pin (Comment as needed)

GpioCtrlRegs.GPBMUX2.bit.GPIO61 = 1; // GPIO61 is MFSRB pin (Comment as needed)

/* Enable internal pull-up for the selected pins */

// Pull-ups can be enabled or disabled by the user.

// This will enable the pullups for the specified pins.

// Comment out other unwanted lines.

// GpioCtrlRegs.GPAPUD.bit.GPIO24 = 0; // Enable pull-up on GPIO24 (MDXB) (Comment as needed)

//GpioCtrlRegs.GPAPUD.bit.GPIO12 = 0; // Enable pull-up on GPIO12 (MDXB) (Comment as needed)

//GpioCtrlRegs.GPAPUD.bit.GPIO25 = 0; // Enable pull-up on GPIO25 (MDRB) (Comment as needed)

//GpioCtrlRegs.GPAPUD.bit.GPIO13 = 0; // Enable pull-up on GPIO13 (MDRB) (Comment as needed)

//GpioCtrlRegs.GPAPUD.bit.GPIO26 = 0; // Enable pull-up on GPIO26 (MCLKXB) (Comment as needed)

//GpioCtrlRegs.GPAPUD.bit.GPIO14 = 0; // Enable pull-up on GPIO14 (MCLKXB) (Comment as needed)

// GpioCtrlRegs.GPAPUD.bit.GPIO3 = 0; // Enable pull-up on GPIO3 (MCLKRB) (Comment as needed)

//GpioCtrlRegs.GPBPUD.bit.GPIO60 = 0; // Enable pull-up on GPIO60 (MCLKRB) (Comment as needed)

// GpioCtrlRegs.GPAPUD.bit.GPIO27 = 0; // Enable pull-up on GPIO27 (MFSXB) (Comment as needed)

//GpioCtrlRegs.GPAPUD.bit.GPIO15 = 0; // Enable pull-up on GPIO15 (MFSXB) (Comment as needed)

// GpioCtrlRegs.GPAPUD.bit.GPIO1 = 0; // Enable pull-up on GPIO1 (MFSRB) (Comment as needed)

//GpioCtrlRegs.GPBPUD.bit.GPIO61 = 0; // Enable pull-up on GPIO61 (MFSRB) (Comment as needed)

/* Set qualification for selected input pins to asynch only */

// This will select asynch (no qualification) for the selected pins.

// Comment out other unwanted lines.

GpioCtrlRegs.GPAQSEL2.bit.GPIO25 = 3; // Asynch input GPIO25 (MDRB) (Comment as needed)

//GpioCtrlRegs.GPAQSEL1.bit.GPIO13 = 3; // Asynch input GPIO13 (MDRB) (Comment as needed)

// GpioCtrlRegs.GPAQSEL2.bit.GPIO26 = 3; // Asynch input GPIO26(MCLKXB) (Comment as needed)

//GpioCtrlRegs.GPAQSEL1.bit.GPIO14 = 3; // Asynch input GPIO14 (MCLKXB) (Comment as needed)

// GpioCtrlRegs.GPAQSEL1.bit.GPIO3 = 3; // Asynch input GPIO3 (MCLKRB) (Comment as needed)

GpioCtrlRegs.GPBQSEL2.bit.GPIO60 = 3; // Asynch input GPIO60 (MCLKRB) (Comment as needed)

// GpioCtrlRegs.GPAQSEL2.bit.GPIO27 = 3; // Asynch input GPIO27 (MFSXB) (Comment as needed)

//GpioCtrlRegs.GPAQSEL1.bit.GPIO15 = 3; // Asynch input GPIO15 (MFSXB) (Comment as needed)

// GpioCtrlRegs.GPAQSEL1.bit.GPIO1 = 3; // Asynch input GPIO1 (MFSRB) (Comment as needed)

GpioCtrlRegs.GPBQSEL2.bit.GPIO61 = 3; // Asynch input GPIO61 (MFSRB) (Comment as needed)

EDIS;

}

void InitXintf32Gpio()

{

EALLOW;

GpioCtrlRegs.GPBMUX2.bit.GPIO48 = 3; // XD31

GpioCtrlRegs.GPBMUX2.bit.GPIO49 = 3; // XD30

GpioCtrlRegs.GPBMUX2.bit.GPIO50 = 3; // XD29

GpioCtrlRegs.GPBMUX2.bit.GPIO51 = 3; // XD28

GpioCtrlRegs.GPBMUX2.bit.GPIO52 = 3; // XD27

GpioCtrlRegs.GPBMUX2.bit.GPIO53 = 3; // XD26

GpioCtrlRegs.GPBMUX2.bit.GPIO54 = 3; // XD25

GpioCtrlRegs.GPBMUX2.bit.GPIO55 = 3; // XD24

GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 3; // XD23

GpioCtrlRegs.GPBMUX2.bit.GPIO57 = 3; // XD22

GpioCtrlRegs.GPBMUX2.bit.GPIO58 = 3; // XD21

GpioCtrlRegs.GPBMUX2.bit.GPIO59 = 3; // XD20

// GpioCtrlRegs.GPBMUX2.bit.GPIO60 = 3; // XD19

// GpioCtrlRegs.GPBMUX2.bit.GPIO61 = 3; // XD18

GpioCtrlRegs.GPBMUX2.bit.GPIO62 = 3; // XD17

GpioCtrlRegs.GPBMUX2.bit.GPIO63 = 3; // XD16

GpioCtrlRegs.GPBQSEL2.bit.GPIO48 = 3; // XD31 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO49 = 3; // XD30 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO50 = 3; // XD29 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO51 = 3; // XD28 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO52 = 3; // XD27 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO53 = 3; // XD26 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO54 = 3; // XD25 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO55 = 3; // XD24 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO56 = 3; // XD23 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO57 = 3; // XD22 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO58 = 3; // XD21 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO59 = 3; // XD20 asynchronous input

// GpioCtrlRegs.GPBQSEL2.bit.GPIO60 = 3; // XD19 asynchronous input

// GpioCtrlRegs.GPBQSEL2.bit.GPIO61 = 3; // XD18 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO62 = 3; // XD17 asynchronous input

GpioCtrlRegs.GPBQSEL2.bit.GPIO63 = 3; // XD16 asynchronous input

InitXintf16Gpio();

}

Any help is help is appreciated,

Curtis Randall