Other Parts Discussed in Thread: OPA350

Tool/software: Code Composer Studio

Hi,

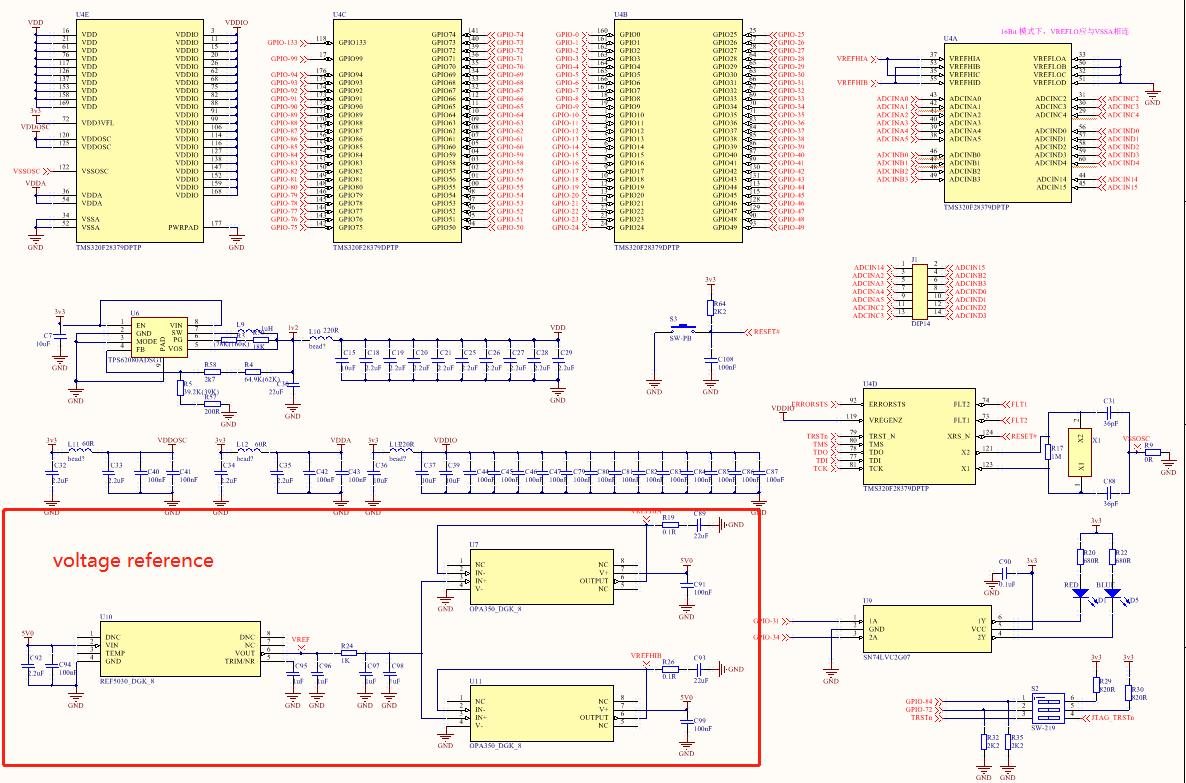

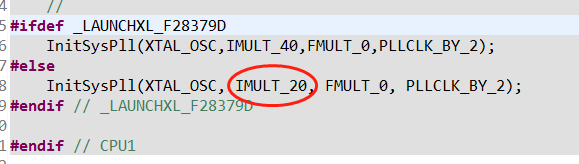

I got some questions in TMS320F38279D ADC program and hardware using differential mode(16bit).

The sinusodial signal with about 1.9V Vpp and 1KHz frequence was converted into digital signal by using the adc module in the board LAUNCHXL-F28379D. The running result shows below. It can be seen that the waveform get phase loss in the black dotted line box. Why does it happened?

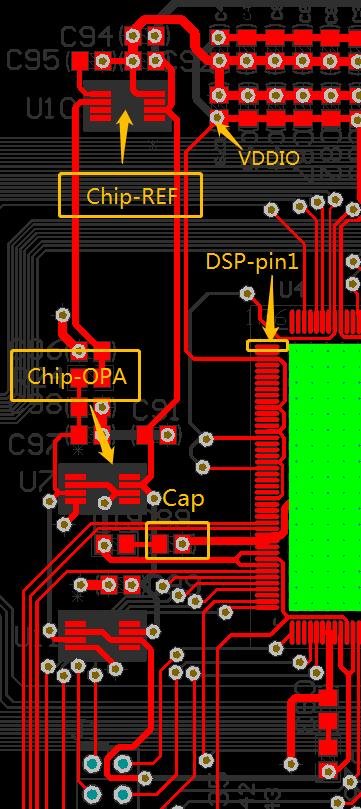

I try to make a circuit board using master chip TMS3220F28379D to realize A/D convertion. The A/D test I made using the same program. The result compared to LAUNCHXL-F28379D result is show below. It seems that it is quite a bit wrong except the Vpp. What do I missed?

Best regards,

DITNY.