Dear C2000 expert

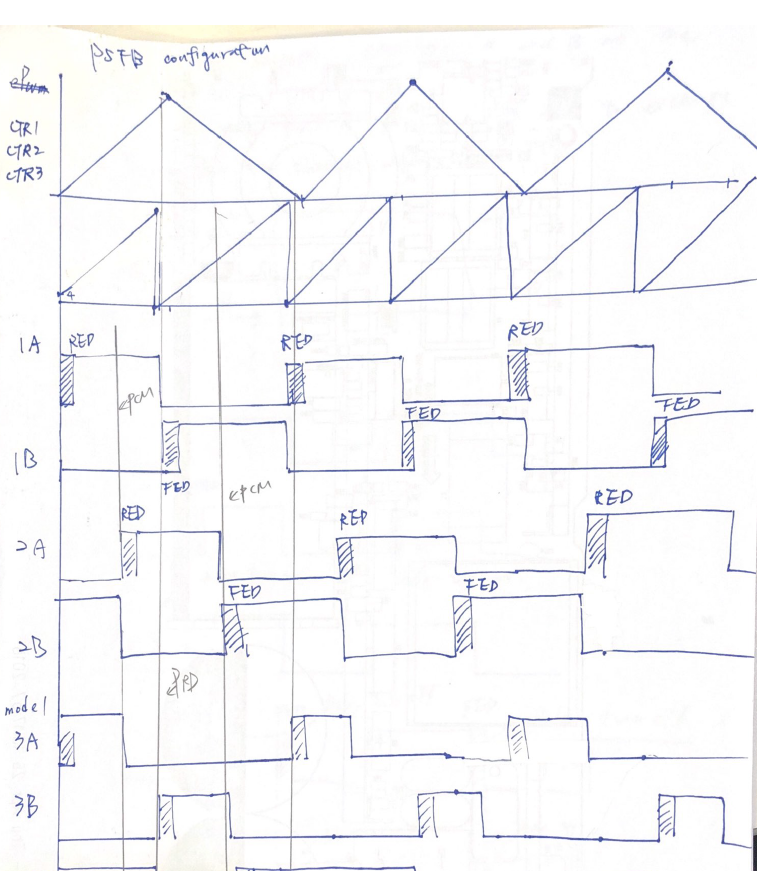

We are trying to use CMPSS to provide CTRIP signal in order to generate the T1 /T2 event.

The CTRIPH was selected as CTRIP_FILTER

Generally the output was look good.The 2A/2B was turn on / turn off at the T1 event (T1D/ T1U)

When we put the configuration at close loop to do PSFB control , we fund the 2A/2B signal was shoot through.

We look at the EPWM open loop and we fund such wrong was impacted by CTRIP signal waveform.

The B channel wil work not correctly and get crasy.

We try to simplize the issue. We set PWMA and PWMB channel was all the same configuration and the dead time set to zero.

We the the PWMB signal was becoming uncontrollable when the T1 event was triggered.

PWMB was change the state after the CTRIP sinal was low. We also fund the PWM module was getting uncontrollable until we disable the T1 event.

I didnot know why the PWMB signal become unexpected waveform.

We also find the strange behavior when we try to change the OUTSWAP(DB module) to verify the PWMA and PWMB at this kind of condition.

The OUTSWAP( DB module) was not follow the value we changed until we disable the T1 event source.

So , we would like ask

1. the DC sub moulde was level trigger or edge trigger?

2. What was the potential issue to affect the ePWM module as this condition??

Thanks

BR

Brian