Other Parts Discussed in Thread: TMDSHSECDOCK

Dear Sirs,

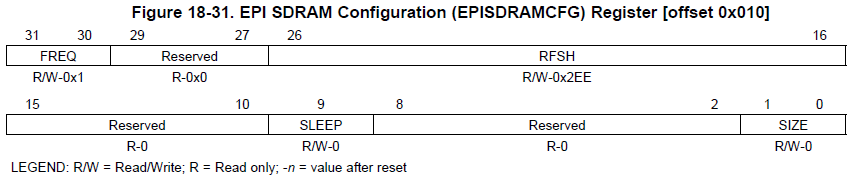

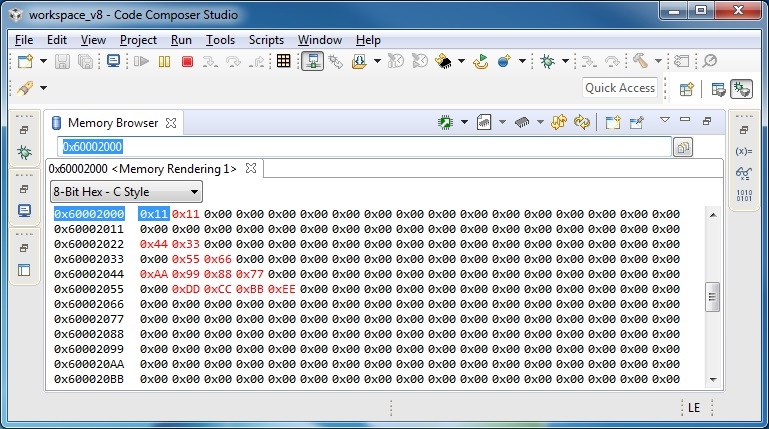

We have added SDRAM to the EPI as per the Table 18-1 of the SPRUHE8D.pdf data sheet. The SDRAM chip is we used is a IS42S16800F 128Mbit (8M x 16). We placed this at a base address of 0x60000000. We used the SDRAM software example in the Control Suite. It works fine for even addresses when accessing 16 bit and 32 bit data sizes. However, we cannot write 8 bit data at odd addresses. Below is a debug output example of our problem:

Wrote 0 to address 60002000 Wrote 1 to address 60002001 Wrote 2 to address 60002002

Writing 3 to address 60002003

Read 0 from address 60002000 Read 0 from address 60002001 Read 2 from address 60002002

Read 2 from address 60002003

Thank your for your help.