Part Number: TMS320F280049

Hi,

we would like to use the PGA with AC signals.

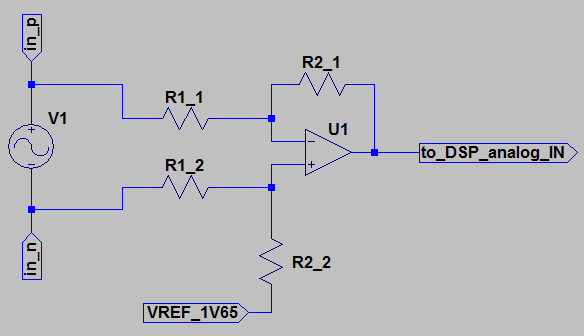

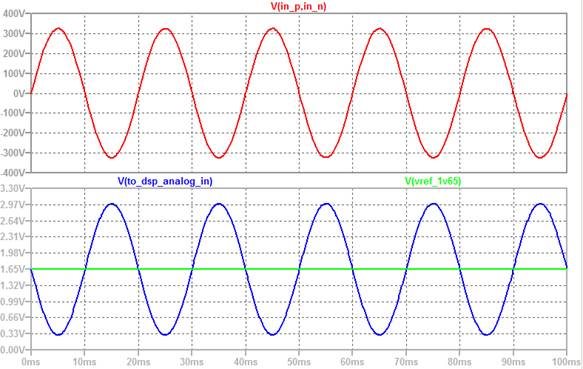

Typically, they have a 1.65V offset and a +-1.65V amplitude to reach the max. 3.3V ADC input.

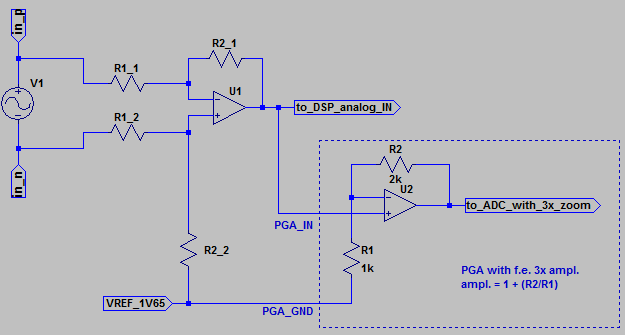

If we now want to measure a signal with 1.65V offset and only 0.2V amplitude, this does not seem to be possible with the current PGA.

We would have to adjust the offset according to the PGA scale.

In addition, the PGA Gain cannot be chosen to be 1 as 3 is the lowest amplification.

The PGA_GND has to be in -50..200mV range - we would need it at 1.65V for the AC signals.

This makes the PGA not suited for AC signals.

Any hints or solutions? Or do we have to wait for this feature to be implemented in a future device?