I am running 2 SCI buses, B and C on the TMS320F28379. When running the board, both have the same settings, shown below:

// configure SCICCR for SCI-C

ScicRegs.SCICCR.bit.STOPBITS = 0; // 1 stop bit

ScicRegs.SCICCR.bit.PARITY = 0; // odd parity

ScicRegs.SCICCR.bit.PARITYENA = 0; // parity disabled

ScicRegs.SCICCR.bit.LOOPBKENA = 0; // loopback disabled

ScicRegs.SCICCR.bit.ADDRIDLE_MODE = 0; // idle-line mode protocol selected

ScicRegs.SCICCR.bit.SCICHAR = 7; // 8 data bits

// configure SCICTL1 for SCI-C

ScicRegs.SCICTL1.bit.RXERRINTENA = 0; // receive error interrupt disabled

ScicRegs.SCICTL1.bit.SWRESET = 0; // software reset enabled (active low) while configuring

ScicRegs.SCICTL1.bit.TXWAKE = 0; // SCI TX Wake feature disabled

ScicRegs.SCICTL1.bit.SLEEP = 1; // Sleep mode enabled

ScicRegs.SCICTL1.bit.TXENA = 1; // enable TX

ScicRegs.SCICTL1.bit.RXENA = 1; // enable RX

// configure SCICTL2 for SCI-C

ScicRegs.SCICTL2.bit.RXBKINTENA = 1; // enable receiver-buffer/break interrupt

ScicRegs.SCICTL2.bit.TXINTENA = 0; // disable TX ready interrupt

// configure SCIHBAUD & SCILBAUD for SCI-C

Uint16 brr = 64;// = (Uint16) round(LSPCLK / (SCIC_RS485_BAUD_RATE * 8.0) - 1);

ScicRegs.SCIHBAUD.all = brr >> 8; // Baud Rate = 125k

ScicRegs.SCILBAUD.all = brr & 0xFF; // Baud Rate = 125k

// configure SCIFFTX for SCI-C

ScicRegs.SCIFFTX.bit.SCIRST = 1; // SCI FIFO can resume transmit and receive

ScicRegs.SCIFFTX.bit.SCIFFENA = 1; // SCI FIFO enhancements are enabled

ScicRegs.SCIFFTX.bit.TXFIFORESET = 0; // Reset the TX FIFO pointer to zero and hold in reset while configuring

ScicRegs.SCIFFTX.bit.TXFFIENA = 0; // disable transmit FIFO interrupts

ScicRegs.SCIFFTX.bit.TXFFIL = 0; // set transmit FIFO interrupt level bits to 0

// configure SCIFFRX for SCI-C

ScicRegs.SCIFFRX.bit.RXFIFORESET = 0; // Reset the RX FIFO pointer to zero and hold in reset while configuring

ScicRegs.SCIFFRX.bit.RXFFIENA = 1; // Receive FIFO interrupt enable

ScicRegs.SCIFFRX.bit.RXFFIL = 1; // Set receive FIFO interrupt levels bit to 1

// configure SCIFFCT for SCI-C

ScicRegs.SCIFFCT.bit.CDC = 0; // disable auto-baud alignment

ScicRegs.SCIFFCT.bit.FFTXDLY = 0; // set FIFO transfer delay to 0

// Relinquish SCI from Reset

ScicRegs.SCICTL1.bit.SWRESET = 1; // disable software reset

ScicRegs.SCIFFTX.bit.TXFIFORESET = 1; // disable TX FIFO reset

ScicRegs.SCIFFRX.bit.RXFIFORESET = 1; // disable RX FIFO reset

With the same thing on SCIB.

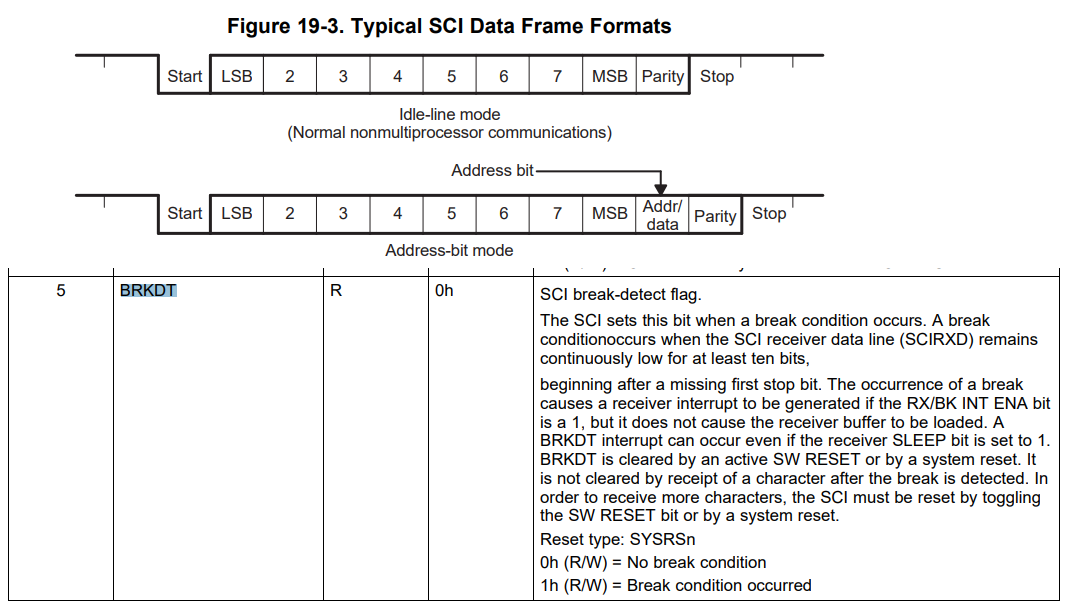

SCIB works appropriately, however I cannot detect any activity with SCIC. This is because after some amount of time the status error flag goes high for BRKDT.

This occurs again if I do a SWRESET on the device, and continues to do so.

The error occurs even if no input is being applied and the RX line is continuously low.

What exactly does this error mean in this case?