Tool/software: Code Composer Studio

I can use a 16 bit extend ram ,when my program like the below. (int is 16 bit )

int *T;

int T1=0;

T= 0x300000;

*T = 1 ;

*(T+1) = 2;

T1= *T;//**************T1=1;

T1= *(T+1);//*************T1=2;

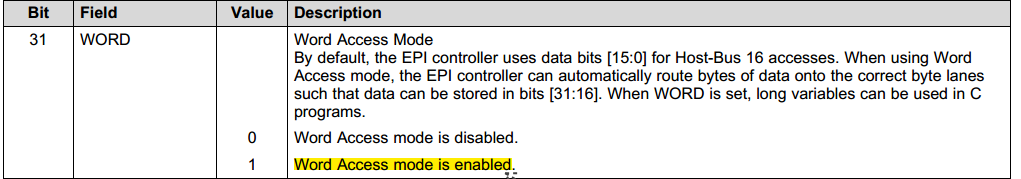

but if my program like this , it will be worry.(long is 32bit )

long *T;

long T1=0;

T= 0x300000;

*T = 0x1234567 ;

*(T+1) = 0x2345678;

T1= *T;//*****************T1=0x 4567 0000

T1= *(T+1);//*********** T1=0x 5678 0000

please help me solve the problem ,thank you