Hi Experts,

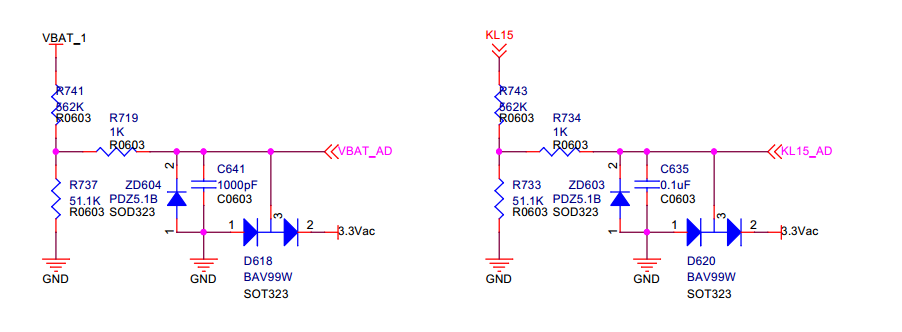

Customer wonders if the ADC sampling hardware need to be optimized, for example reducing R741 & R743 value, because there is abnormal phenomenon happening in the below situation.

As the below picture shown, the two sampling circuits with same structure and components, when put 12V DC source to both VBAT_1 and KL_15,

1) Connected the VBAT_AD & KL15_AD pin with MCU, one ADCResult is 1210, while another is 1224, the value of VBAT_AD & KL15_AD corresponds to related ADCResults value, however the actual ADCResults value has a big gap compared with the ideal result value 1241.

2) When disconnect the VBAT_AD & KL15_AD pin with MCU, the VBAT_AD & KL15_AD voltage is correct.

3) As for customer’s requirement, the error of VBAT_1 and KL_15 calculated value by ADCResult should be limited to 0.2V, reflected to ADCResult error is 21 LSB.

Could you please provide some suggestion on this issue, thanks!

ADC sampling circuits

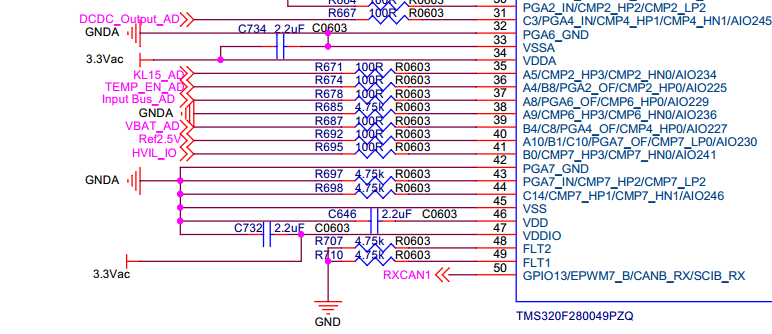

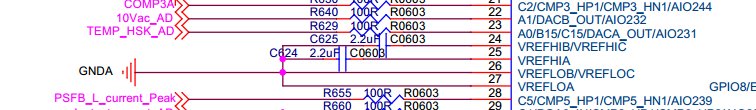

Pin map diagram

- Rayna Wang