Part Number: TMS320F28379D

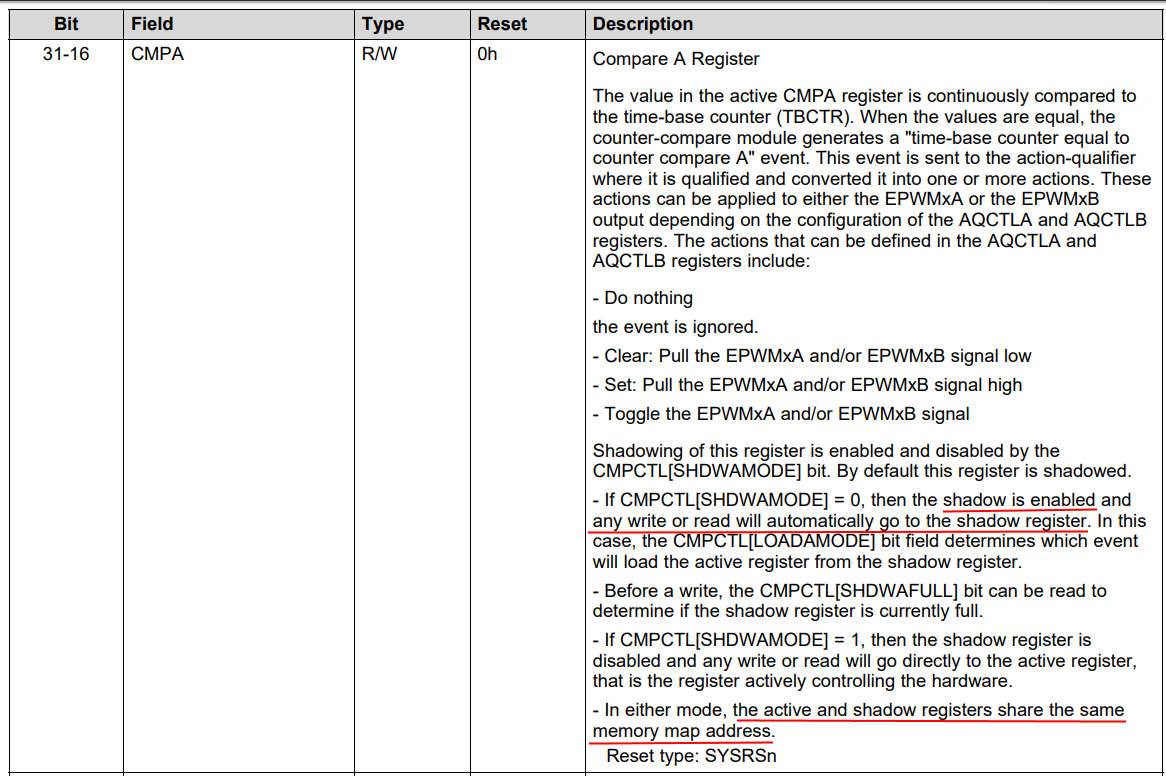

I am using a PWM in up-downcount mode which I want to update with different CMPA-values at both TBCTR = 0 and TBCTR = PRD. So the CMPA-value changes twice per PWM-period. LOADAMODE register is set to "10" which corresponds to "load on either CTR = Zero or CTR = PRD". SHDWAMODE ist set to 0 -> shadow mode, and LOADASYNC is set to 0, that means that shadow to active load of CMPA occurs according to LOADAMODE.

However, although I can see, that the CMPA register toggles between a high value and a low value (since I write at two different occasions per period two distinct values into the CMPA-register), the PWM indicates clearly that only one CMPA-value is taken for the comparison with the time base counter. The behaviour of the PWM is as if a shadow to active register load is done only once and not twice per period. WIth period I mean a full upcount and downcount cycle. LOADAMODE = 0 and LOADAMODE = 1 and LOADAMODE = 2 produce the same PWM.

I tried an immediate update, and there the system behaves as expected. With immediate update I get the PWM I would expect to get with shadow update at TBCTR = 0 or TBCTR = PRD.

The system I am using is entirely deterministic, thus the update of the CMPA value is done exactly at the same time with respect to the time base counter, in fact the update is triggered when the time base counter is zero and when the time base counter equals PRD.

Any ideas what goes wrong here?