Other Parts Discussed in Thread: C2000WARE

Dear team,

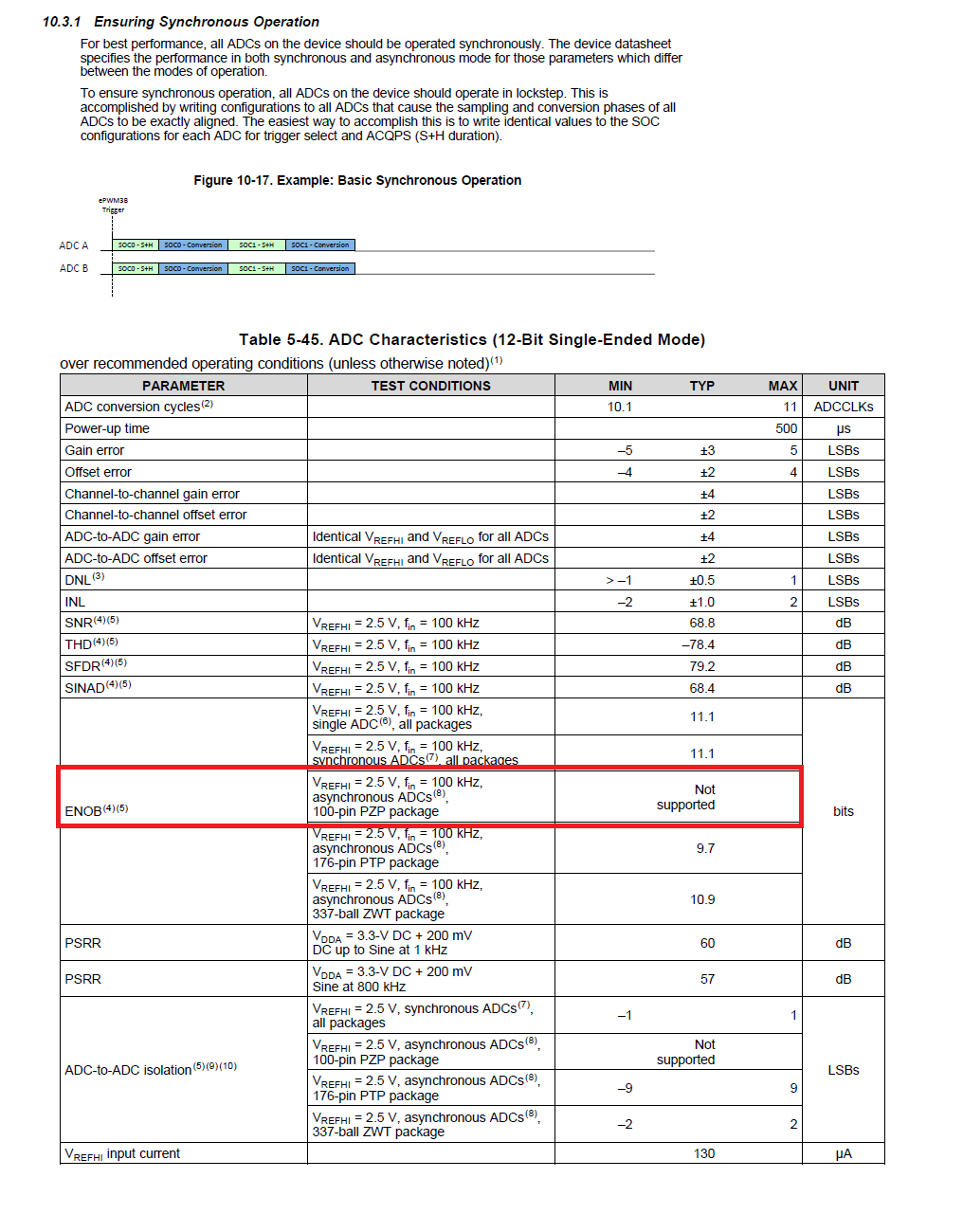

I am using TMS320F2837S controller 100pin package. I have total 14 Analog inputs, 7 for each ADC Core (A and B). In that for one analog channel I need more acquisation window. For rest of the channels I have used 140nS acquisation window, for one channel in ADC A core I used 900nS Acquisation window. So, synchronous operation is not possible. I have tested 140nS aquisation is sufficient and works fine for remaining channels. In datasheet, for 375S 100 Pin 12 bit ADC, in ENOB value, mentioned not supported.

1. Why the limitation is only in 100 pin version?

2. What happens if I go for asynchronous operation in 100 pin package of 375S controller?

3. What happens if there is slight difference (<1 uS) between 2 ADC cores conversion?