Hi,

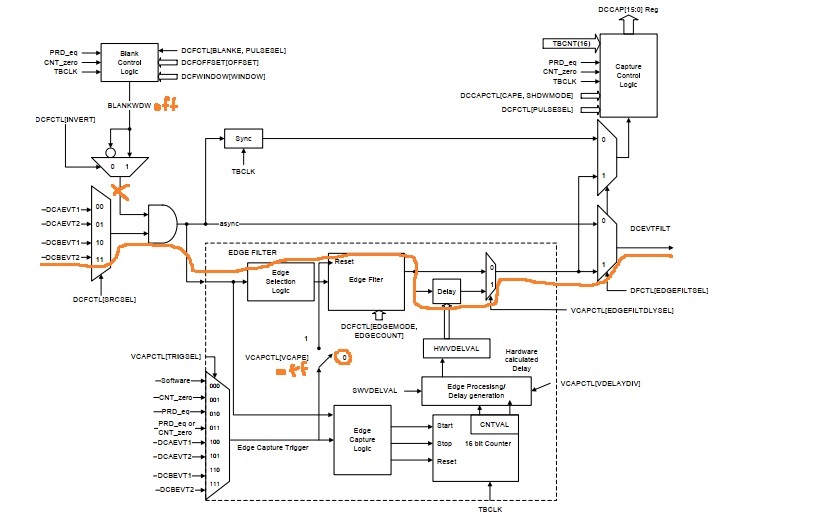

I'm trying to add a delay to the DCBEVT2 signal using Valley Switching Submodule to generate a delayed DCEVTFILT.

Capture features of the Valley Switching Submodule is not useful for my application.

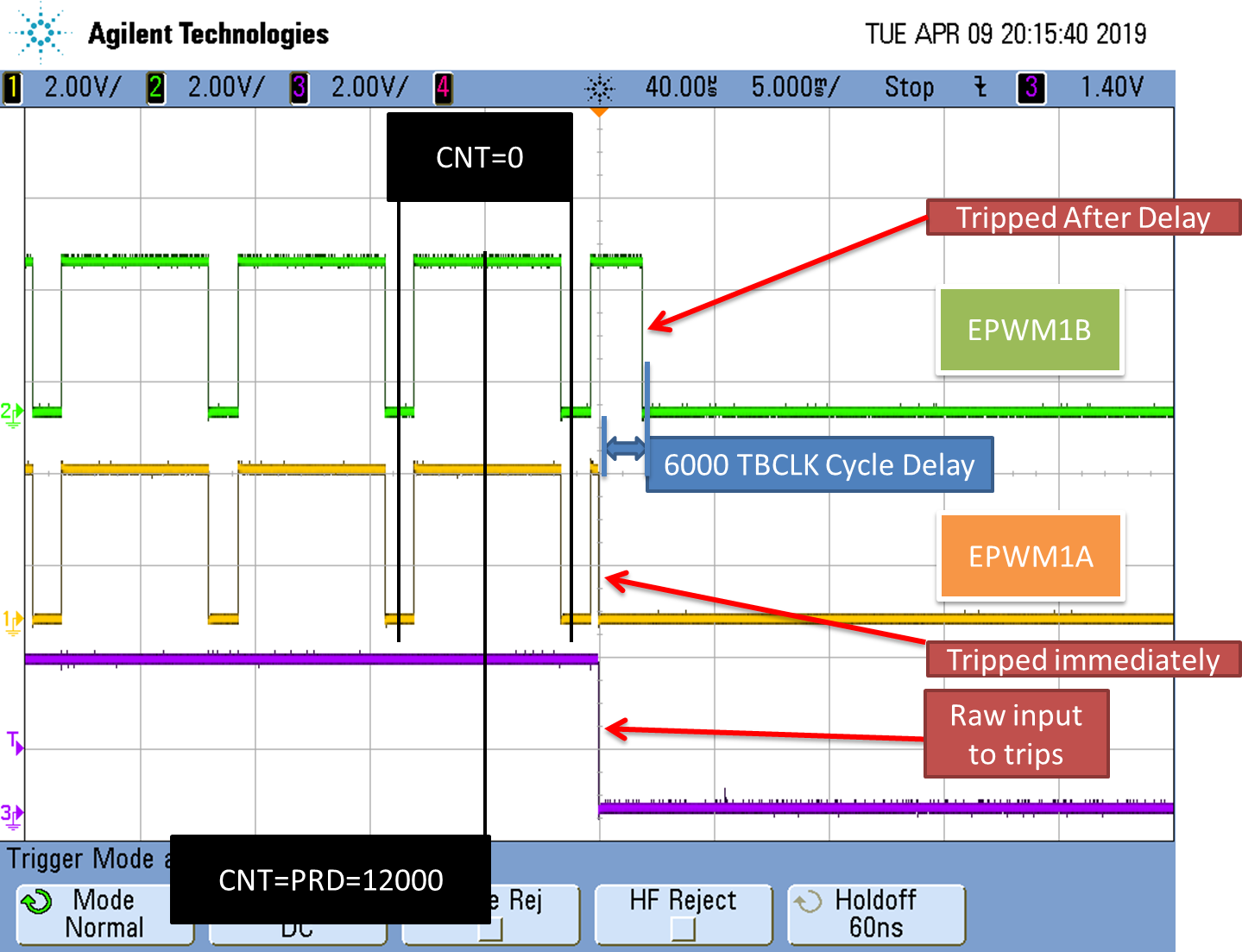

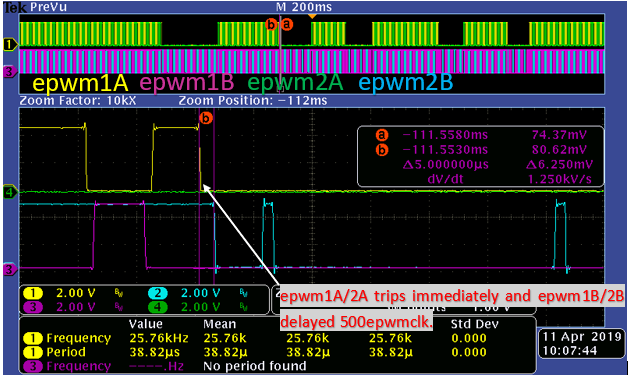

In my configuration DCAEVT2 and DCBEVT2 generated by Cmpss comparators. DCAEVT2 signal trips ePWMA immediately.

DCEVTFILT should trip ePWMB's off after some delay. I thought that HWVDELVAL feature of the Valley Switching may be used for this purpose.

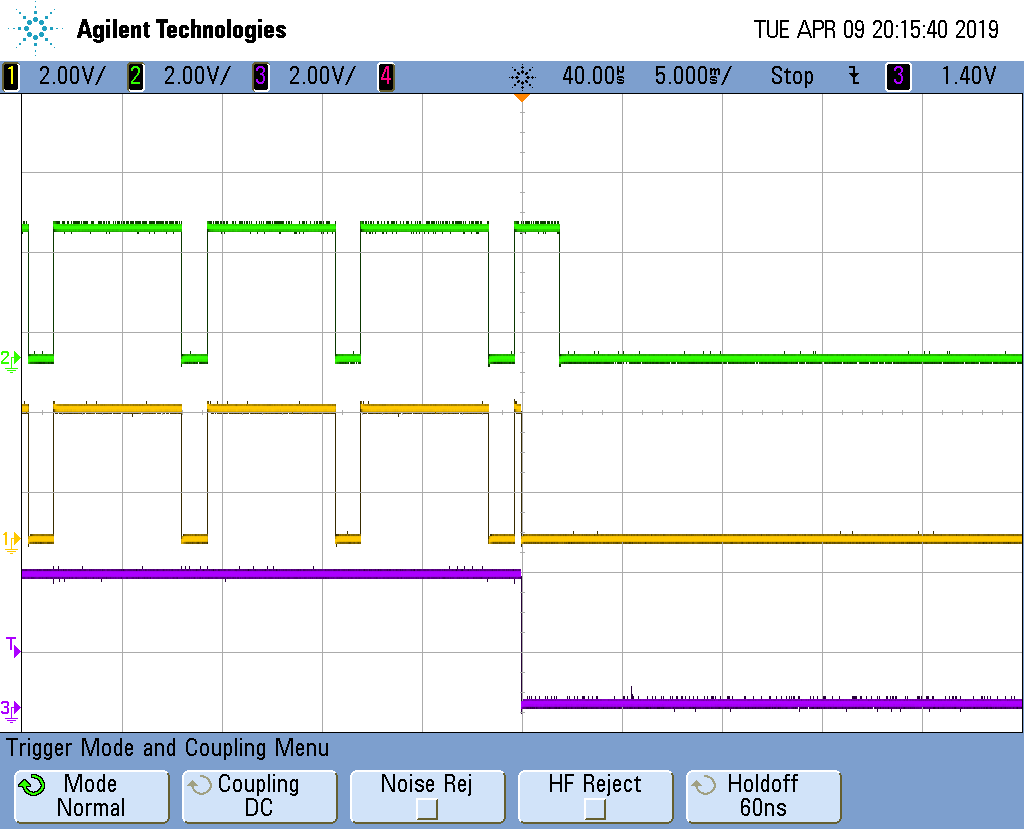

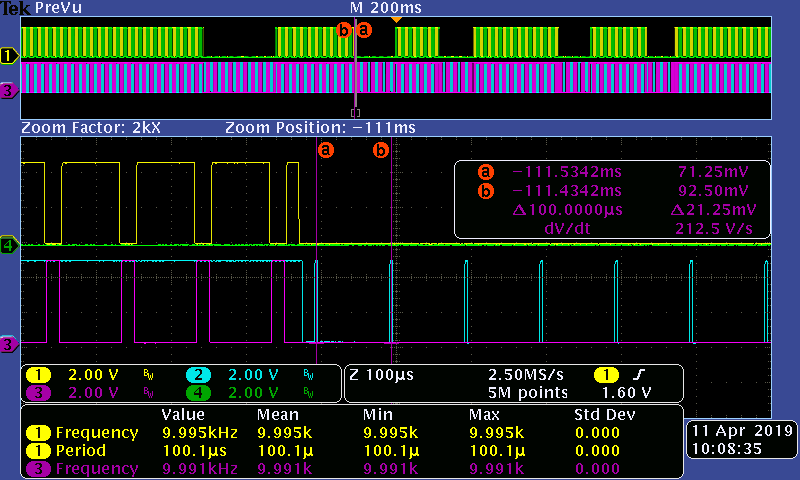

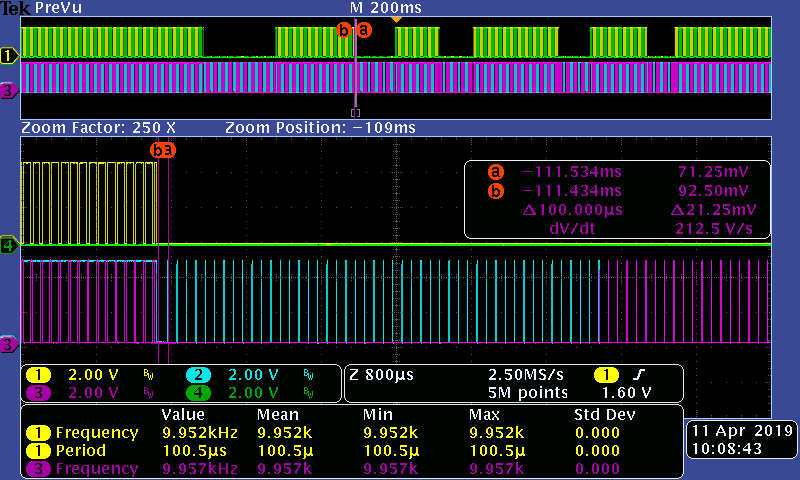

DCAEVT2 and DCBEVT2 trips epwmA/B off successfully but I cannot see a delay on the epwmB.

Here is my configuration of valley switching section;

EPWM_PTR[epwm_num]->DCFCTL.bit.BLANKE = 0; // Blanking window is disabled

EPWM_PTR[epwm_num]->DCFCTL.bit.SRCSEL = 3; // Source Is DCBEVT2 Signal

EPWM_PTR[epwm_num]->DCFCTL.bit.EDGEFILTSEL = 1; // Edge Filter Selected

EPWM_PTR[epwm_num]->DCFCTL.bit.EDGEMODE = 1; // High to Low Edge, cmpss generates high to low signal

EPWM_PTR[epwm_num]->DCFCTL.bit.EDGECOUNT = 0;

EPWM_PTR[epwm_num]->DCCAPCTL.bit.CAPE = 0; // TBCTR Counter Capture Disable

EPWM_PTR[epwm_num]->VCAPCTL.bit.VCAPE = 0; //0; // Valley capture disable, check!! try 1 didnt worked

EPWM_PTR[epwm_num]->VCAPCTL.bit.VDELAYDIV = 0; // HWVDELVAL = SWVDELVAL

EPWM_PTR[epwm_num]->VCAPCTL.bit.EDGEFILTDLYSEL = 1; // HWDELAYVAL delay applied to the edge filter output

EPWM_PTR[epwm_num]->SWVDELVAL = 1000; // Delay Value

Here is my control path;

Configuration provides HWVDELVAL = SWVDELVAL, so the SWVDELVAL value should adjust the delay.

How can I add delay DCBEVT2 with respect to DCAEVT2?

Regards,

Cem.