Hi,

There's a doubt about SPI timing.

After filling the FIFO (for example, one word) to initiate a transmit, when can SPI CLK have the first pulse output? We found that, it was different in different baud rate.

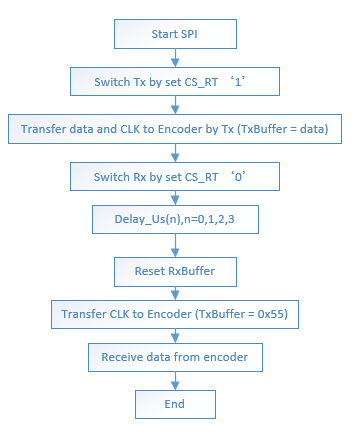

The SPI is used to connect a slave device, which has strict delay request.

Thanks a lot.

Br, Jordan