Other Parts Discussed in Thread: C2000WARE

Hi Champs,

Here is a question about the RX interrupt of SCI.

I am doing an experiment on controlcard based on Example_2803xSci_FFDLB_int. I connected TX and RX on card rather than using internal loopback to simulate the SCI communication between 2 MCUs. In the RX interrupt, I toggle a GPIO to indicate a interrupt. Here is what I observed:

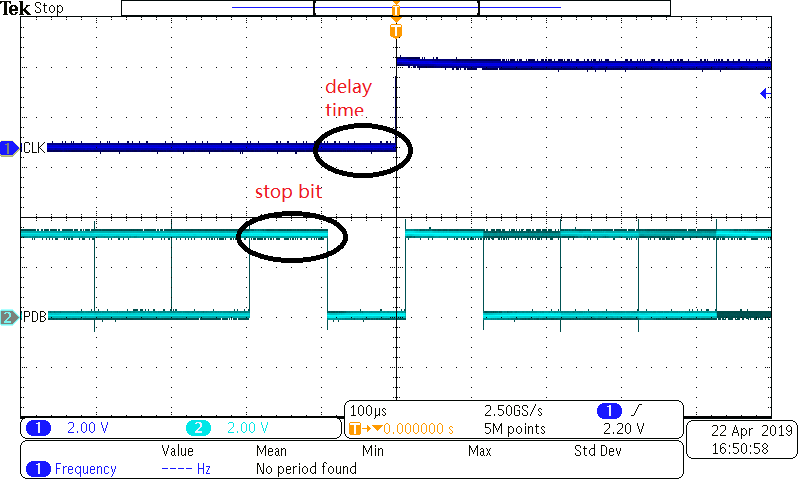

As shown in the picture, after the stop bit, there is a 100us delay before the GPIO is toggled(9600 baud-rate). Is RX designed to be triggered one bit after the stop bit? I only used 1 stop bit. The similar result is also observed by my customer.The source code of RX isr is as below:

_interrupt void

sciaRxFifoIsr(void)

{

Uint16 i;

for(i=0;i<2;i++)

{

rdataA[i]=SciaRegs.SCIRXBUF.all; // Read data

}

for(i=0;i<2;i++) // Check received data

{

if(rdataA[i] != ( (rdata_pointA+1) & 0x00FF) )

{

// error();

}

}

rdata_pointA = (rdata_pointA+1) & 0x00FF;

SciaRegs.SCIFFRX.bit.RXFFOVRCLR=1; // Clear Overflow flag

SciaRegs.SCIFFRX.bit.RXFFINTCLR=1; // Clear Interrupt flag

PieCtrlRegs.PIEACK.all|=0x100; // Issue PIE ack

GpioDataRegs.GPATOGGLE.bit.GPIO0 =1;

}