Part Number: TMS320F280049

Tool/software: Code Composer Studio

hi,

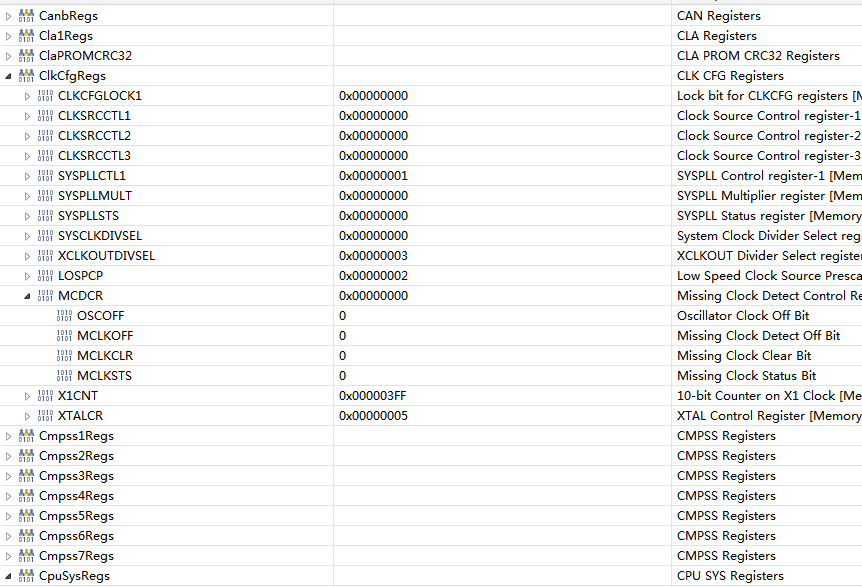

We are facing a question about Crystal oscillator of 0049.

the figure shows how we connect oscillator and c2000,

if we short the Capacitor, our C2000 would enter abnormal states:

- enter Interrupt_defaultHandler

- enter NMI interrupt, Flag shows RAM, Flash, CLB have faults

we hope to know, why these two states happened? why NMI didn't show CLK has fault?

Thank you ~