Tool/software: Code Composer Studio

I am trying to interface between TMS320F28377D and W5500 (WIZNET, Hardware TCP/IP IC).

I spent a lot of time for interfacing with them. But, I have in difficulty.

The below code is my code for SPIa module setting.

void Spia_init()

{

EALLOW;

DevCfgRegs.CPUSEL6.bit.SPI_A = 0; // select CPU1

CpuSysRegs.PCLKCR8.bit.SPI_A = 1; //select CPU Clock/

// GPIO_setting.

GpioCtrlRegs.GPBPUD.bit.GPIO54 = 0; // Enable pull-up on GPIO16 (SPISIMOA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO54 = 3; // Asynch input GPIO16 (SPISIMOA)

GpioCtrlRegs.GPBGMUX2.bit.GPIO54=0;

GpioCtrlRegs.GPBMUX2.bit.GPIO54 = 1; // Configure GPIO16 as SPISIMOA

GpioCtrlRegs.GPBPUD.bit.GPIO55 = 0; // Enable pull-up on GPIO17 (SPISOMIA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO55 = 3; // Asynch input GPIO17 (SPISOMIA)

GpioCtrlRegs.GPBGMUX2.bit.GPIO55=0;

GpioCtrlRegs.GPBMUX2.bit.GPIO55 = 1; // Configure GPIO17 as SPISOMIA

GpioCtrlRegs.GPBPUD.bit.GPIO56 = 0; // Enable pull-up on GPIO18 (SPICLKA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO56 = 3; // Asynch input GPIO18 (SPICLKA)

GpioCtrlRegs.GPBGMUX2.bit.GPIO56=0;

GpioCtrlRegs.GPBMUX2.bit.GPIO56 = 1; // Configure GPIO18 as SPICLKA

GpioCtrlRegs.GPBPUD.bit.GPIO57 = 0; // Enable pull-up on GPIO57 (SPISTEA)

GpioCtrlRegs.GPBQSEL2.bit.GPIO57 = 3; // Asynch input GPIO57 (SPISTEA)

GpioCtrlRegs.GPBGMUX2.bit.GPIO57=0;

GpioCtrlRegs.GPBMUX2.bit.GPIO57 = 1; // Configure GPIO18 as SPICLKA

GpioCtrlRegs.GPAPUD.bit.GPIO23=0;

GpioCtrlRegs.GPAQSEL2.bit.GPIO23 = 3;

GpioCtrlRegs.GPAGMUX2.bit.GPIO23 = 0x0; // RST PIN for W5500

GpioCtrlRegs.GPAMUX2.bit.GPIO23 = 0x0;

EDIS;

SpiaRegs.SPICCR.bit.SPISWRESET = 0;

SpiaRegs.SPICCR.bit.CLKPOLARITY =1; // falling edge data transmission

SpiaRegs.SPICCR.bit.SPICHAR =7; //8-bit char

SpiaRegs.SPICTL.all = 0x0006; // Enable master mode, normal phase, Enable talk

SpiaRegs.SPIBRR.all = 0x001F; // Baud rate = LSPCLK/(BRR+1)

SpiaRegs.SPIFFTX.all = 0xE040; //Transmit registers

SpiaRegs.SPIFFRX.all = 0x2041; //Read registers

SpiaRegs.SPIFFCT.all = 0x00; // Transmit delay = no delay

SpiaRegs.SPIPRI.bit.FREE=1;

SpiaRegs.SPICCR.bit.SPISWRESET = 1;

}

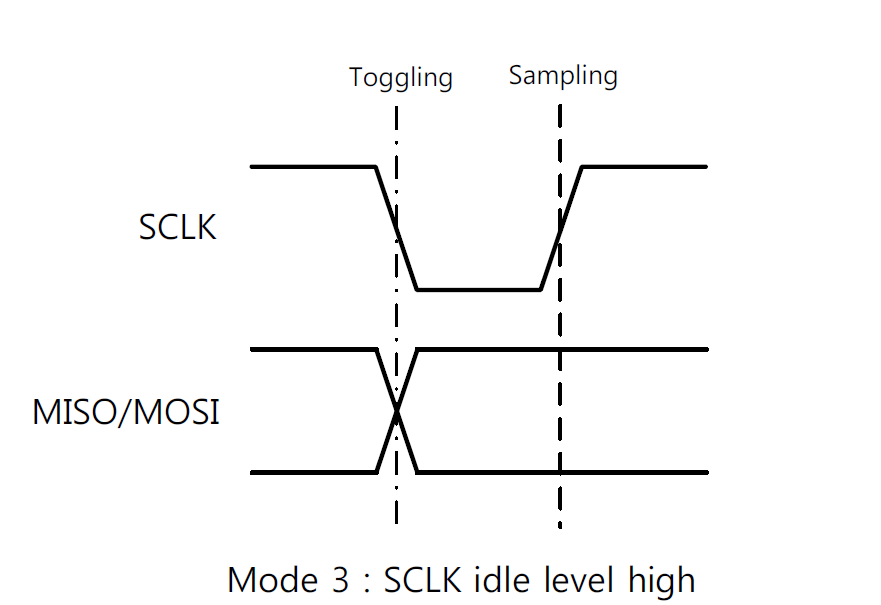

With aformentioned code, I have tried to confirm if the interface with W5500 is working well or not. Actually I expected what I would get wanted data If I send a certain command message (24bit) to W5500 as shown in below figure (from W5500 data sheet).

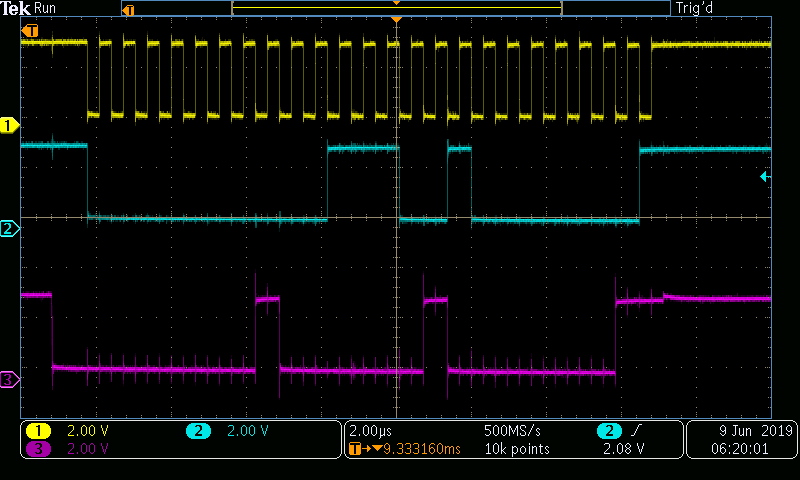

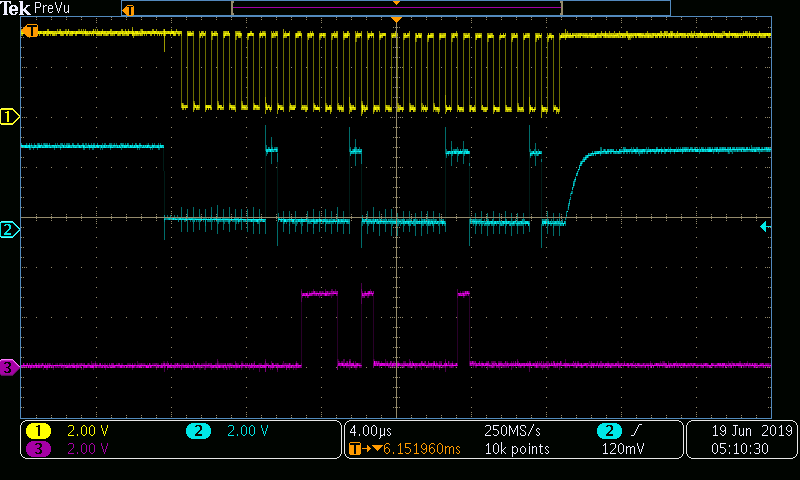

However, in my case, I failed to get data as shown in below figure (Ch. 1 (Yellow Line) : SPI_CLK, Ch.2 (Light Blue Line) : SPI_MOSI, Ch.3(Dark purple Line) : SPI_MISO

I don't understand a few situation related to the results

1) why the SPI_CLK and /SPITE signal finish before data is received from W5500.

2) What is the unwanted signal during Command transmission from TMS32028377D.

To solve the problem, could you give me review my SPIa setting code and any solution?

best regards

Sung-Ho Lee