Dear Sir ,

We are using the F2837XD in our prototype under development , and we require some function in code to execute from the RAM ,the code itself will be load externally by another component (FPGA) which will instruct the DSP to load it to specific RAM location and to run it.

a. for test purpose i have created such function as follow (the function will be place in section .control )

#pragma CODE_SECTION(servo_init,".control");

void servo_init(void)

{

...

}

b. in the linker file i assign RAMGS0123 (it is RAMGS0-RAMGS3) to page 0 to be as code memory , and .control section to reside in RAMGS0123

MEMORY

{

PAGE 0 :

RAMGS0123 : origin = 0x00C000, length = 0x004000

...

..

PAGE 1 :

}

SECTIONS

{

....

.control:{

Control.obj(.control,.econst,.text,.switch,.cinit,fpga_in)

IDM_ICM_HAL.obj(.servo_hal,.econst,.text,.switch,.cinit)

} >RAMGS0123 PAGE = 0, ALIGN(4)

}

c.for debug purpose i have loaded the image to the target , and rely on the fact that the debug probe will place my code (servo_init() ) in the proper place in the RAM (RAMGS0123)

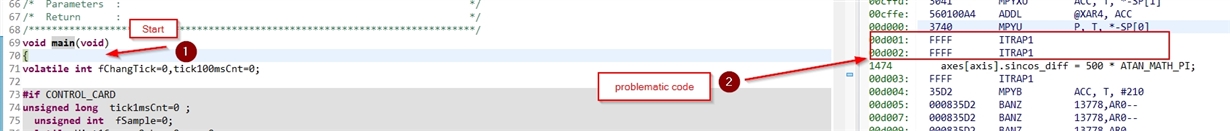

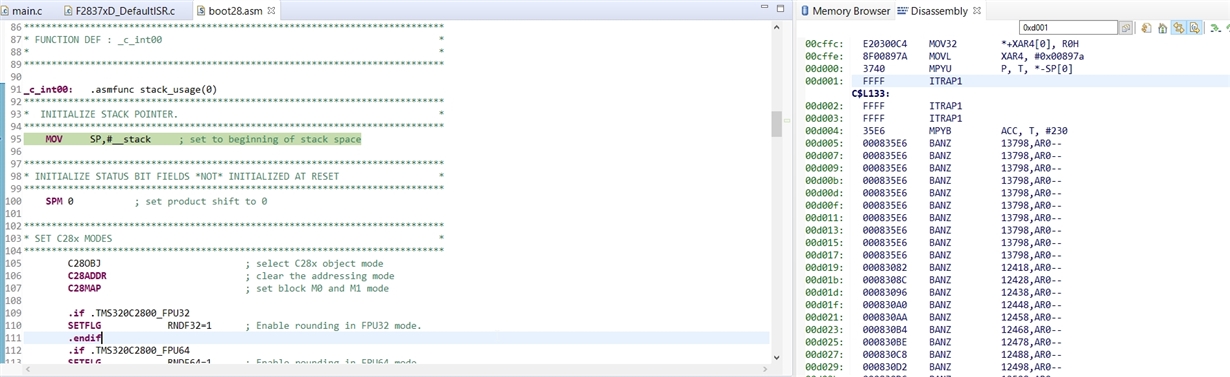

d.when i run the code and enter servo_init() few lines are executed , but i have encounter TRAP (illegal OP code ) , when debugging again i have looked at disassembly view and found the following

in the picture below the assembly command is executed and then two ITRAP1 command are inserted , which i don't quite understand why ?

is this normal behavior ? am i missing something in the linker command file ?