I am attempting to implement a data transfer of characters from CPU1 to CPU2 using IPC. I found this example in the datasheet but I cannot get the process to work. Here is what the data sheet is saying, and I am using:

Here is an example of how to use these features together. CPUx needs some data from CPUy's LS RAM. The data is at CPUy address 0x9400 and is 0x80 16-bit words long. The protocol could be implemented like this: – CPUx writes 0x1 to IPCSENDCOM, defined in software to mean "copy data from address".

It writes the address (0x9400) to IPCSENDADDR and the data length (0x80) to IPCSENDDATA.

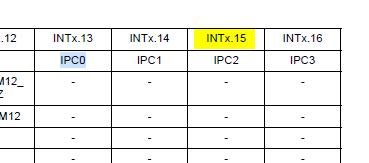

– CPUx writes to IPCSET[3] and IPCSET[16]. Here, IPC flag 3 is configured to send an interrupt and IPCSET[16] is defined in software to indicate an incoming command. CPUx begins polling for IPCFLG[3] to go low.

– CPUy receives the interrupt. In the interrupt handler, it checks IPCSTS, finds that flag 16 is set, and runs a command processor.

– CPUy reads the command (0x1) from IPCRECVCOM, the address (0x9400) from IPCRECVADDR, and the data length (0x80) from IPCRECVDATA.

CPUy then copies the LS RAM data to an empty space in its writable shared memory starting at offset 0x210.

– CPUy writes the shared memory address (0x210) to its IPCLOCALREPLY register. It then writes to IPCACK[16] and IPCACK[3] to clear the flags and indicate completion of the command. CPUy's work is done. – CPUx sees IPCFLG[3] go low. It reads IPCREMOTEREPLY to get the shared memory offset of the

I am using this block of code to attempt to send data to shared ram then will read it on CPU2 but it is not working

SendIpcData((void*)ReceivedChar, 8, 22);

IpcRegs.IPCSENDCOM = 0x1;

IpcRegs.IPCSENDADDR = (void*)ReceivedChar;

IpcRegs.IPCSENDDATA = (8*i);

Am I going about this correctly or am I using the wrong functions?

Thanks in advance.