SIr/Madam,

I have used cmpss module to trigger tripzone in epwm using epwm crossbar.

For that following setting I have done.

AnalogSubsysRegs.CMPHPMXSEL.bit.CMP1HPMXSEL = 1;//O/C-N

Cmpss1Regs.COMPCTL.bit.COMPHSOURCE = NEGIN_DAC;

Cmpss1Regs.COMPDACCTL.bit.SELREF = REFERENCE_VDDA;

Cmpss1Regs.DACHVALS.bit.DACVAL = 1862;// 1.5V

Cmpss1Regs.CTRIPHFILCLKCTL.bit.CLKPRESCALE = 100;

Cmpss1Regs.CTRIPHFILCTL.bit.SAMPWIN = 0x1F;

Cmpss1Regs.CTRIPHFILCTL.bit.THRESH = 30; //3us

Cmpss1Regs.CTRIPHFILCTL.bit.FILINIT = 1;

Cmpss1Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_FILTER;

Cmpss1Regs.COMPCTL.bit.CTRIPOUTHSEL = CTRIP_FILTER;

EPwm1Regs.TZDCSEL.bit.DCBEVT1 = TZ_DCBH_HI;//0x2

EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xF; //DCBHTRIPSEL

EPwm1Regs.TZSEL.bit.DCBEVT1 = 1;

EPwm1Regs.DCBCTL.bit.EVT1SRCSEL = DC_EVT1;

EPwm1Regs.DCBCTL.bit.EVT1FRCSYNCSEL = DC_EVT_ASYNC;

EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1;

EPwmXbarRegs.TRIP7MUX0TO15CFG.bit.MUX0 = 0;

EPwmXbarRegs.TRIP7MUXENABLE.bit.MUX0 = 1;

EPwm1Regs.TZCLR.bit.OST = 1;

EPwm1Regs.TZCLR.bit.CBC = 0;

EPwm1Regs.TZCLR.bit.INT = 1;

System clock = 100Mhz

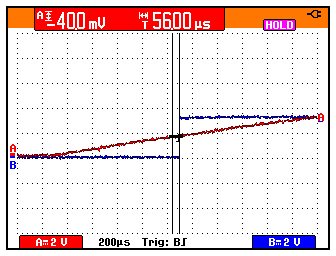

Now when I give slowly rising signal on comparator input, the trip is delayed by 18 milliseconds. And when I give relatively fast signal trip gets delayed only by 56 microseconds.

For your reference i am attaching following images.

Channel A: comparator input

Channel B: Tripzone interrup

When comparator input is changed fast, tripzone gets triggered instantly.

While levels have been set same at 1.5V in both cases.

Channel B: input of comparator

So please tell why this comparator output is delayed by such long time?

Thanks

Rishabh