Other Parts Discussed in Thread: CC2640, TMS320F28035, TMS320F280049

Hi all!

I currently develop a LIN slave stack with the above mentioned controller. The stack shall be compatible with LIN 2.2 and I want to use the LIN module. I have to say the module is quite intuitive and very capable. However currently I have a problem when the transmitted header is not complete (ID missing).

The next header generates then a Parity Error Interrupt and no more ID complete interrupt. The timing between the frames seems to have no effect as I changed the transmission time of the uncorrupted frame.

When reading the technical reference manual I found a passage that the LIN module counts the sync break and sync field length for detecting inconsistent sync field errors. However it seems to not work when the previous header was not completed. Unfortunately this is needed for LIN 2.2 compliance.

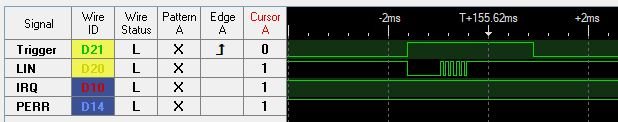

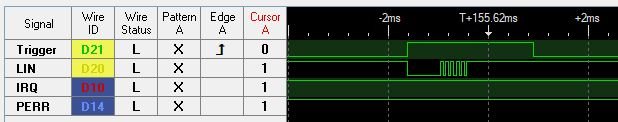

Here is a picture where I have in the incomplete frame header (only Sync Break and Sync Field):

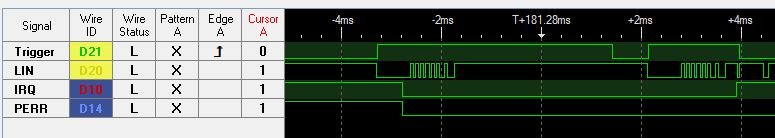

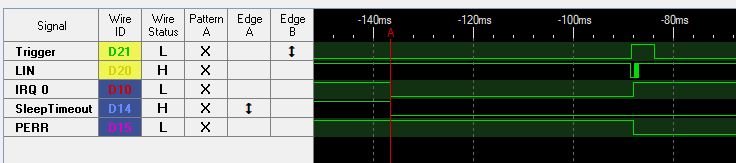

And the following complete header with the parity error but not ID complete interrupt and the next complete header where everything is working and the node is responding again:

As you can see from the timestamps the pause between the incomplete header and the next complete one is already relatively long, so that the module could recover, but it does not.

I have currently active:

SETRXINT, SETIDINT, SETPEINT, SETFEINT, SETNREINT, SETISFEINT, SETCEINT, SETBEINT.

I tried to activate the sync break interrupt despite the remark that it is only available in SCI mode, but of course I didn’t get any additional interrupts.

Perhaps any of you can give me a hint where I can get the information that the LIN module is busy (this would already help tremendously because then I can setup a timeout), or how to get any interrupt for this.

I appreciate any help, ideas and comments,

greetings

Barbara Reiss