Other Parts Discussed in Thread: TLV6001, ISO224, ISO224EVM

Tool/software: WEBENCH® Design Tools

Hello,

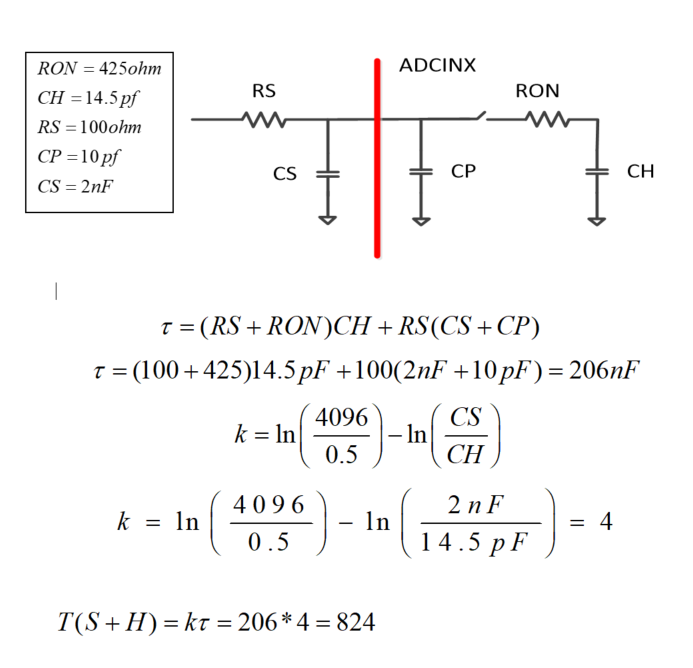

For my experiment I am using switching frequency is 50KHz and ADC sampling frequency should be 4 or 5 times larger than switching frequency. i want to design RC bucket circuit and ACQPS for 200KHZ sampling frequency. i have selected CS 2nF. is it right for 200KHZ sampling frequency? Do is need to increase or decrease CS ? I am not sure if i can increase or decrease CS as sampling frequency goes higher. TI recommends that CS should be at least 10 or 20 times larger than CH. and how can i select RS too? I did the calculation for ACQPS is it right or not ? I still don't understand relationship between ADC sampling and charge circuit bucket circuit