Hi Team,

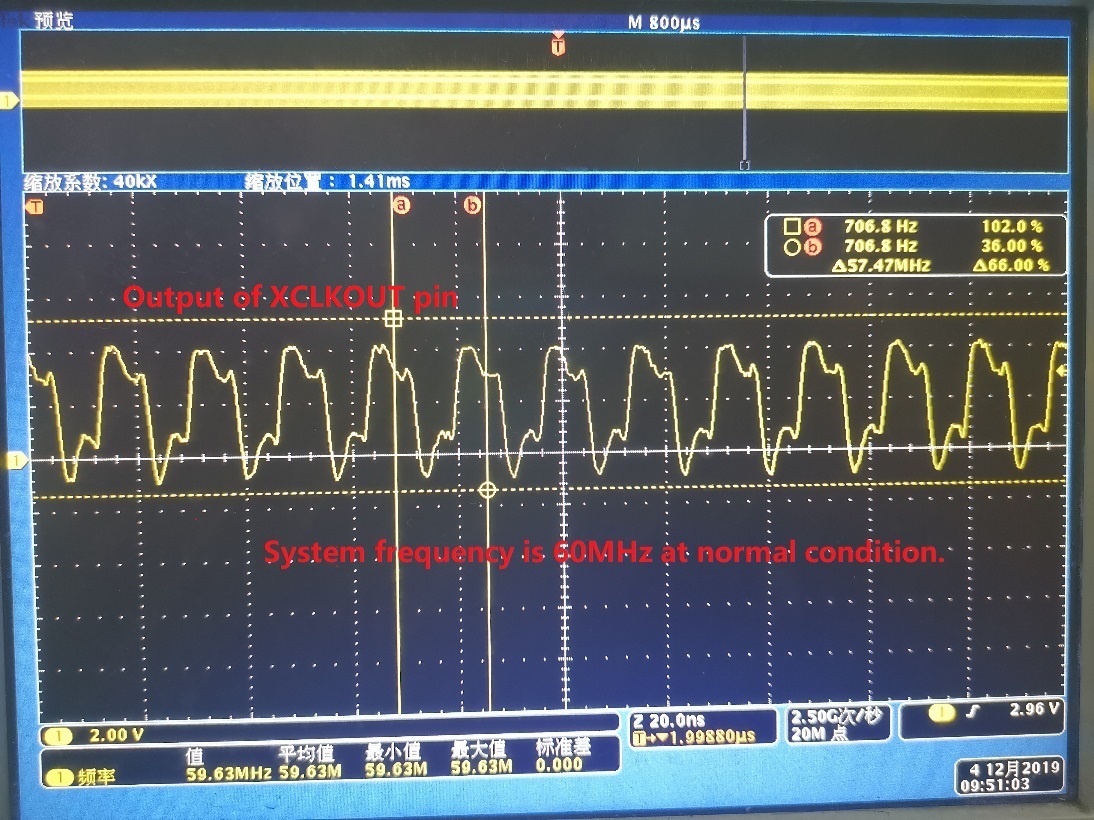

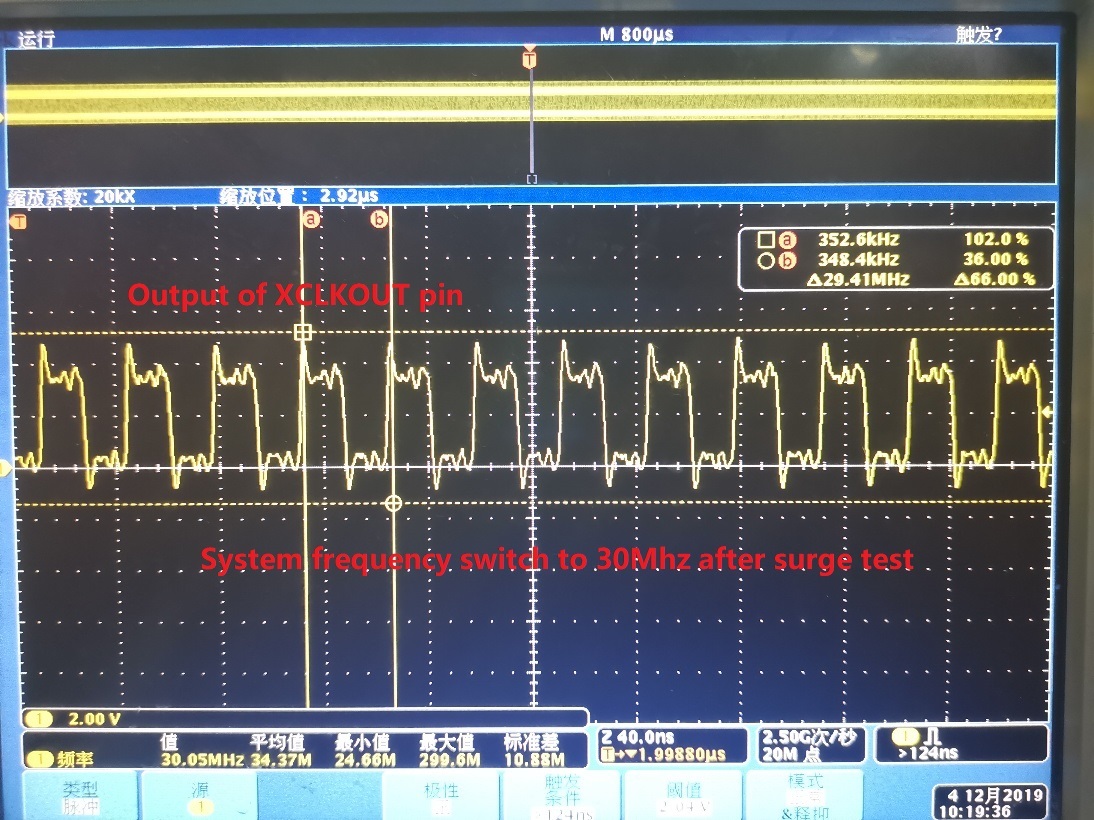

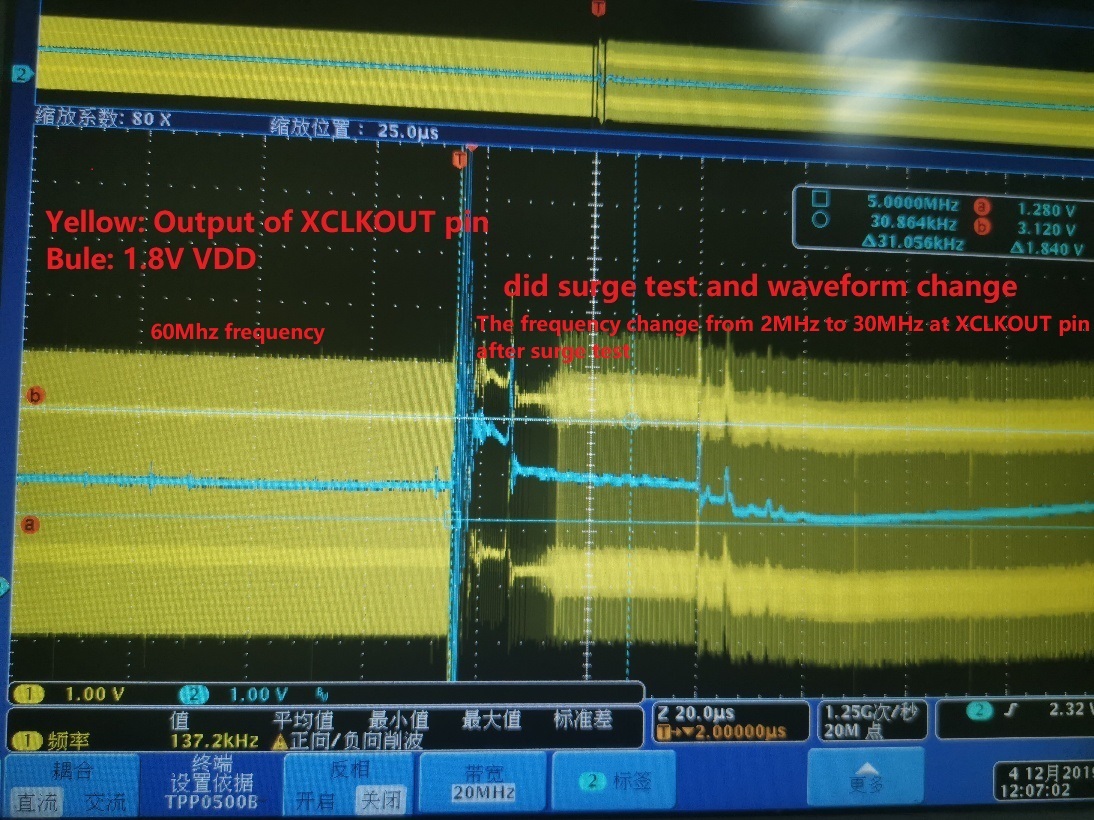

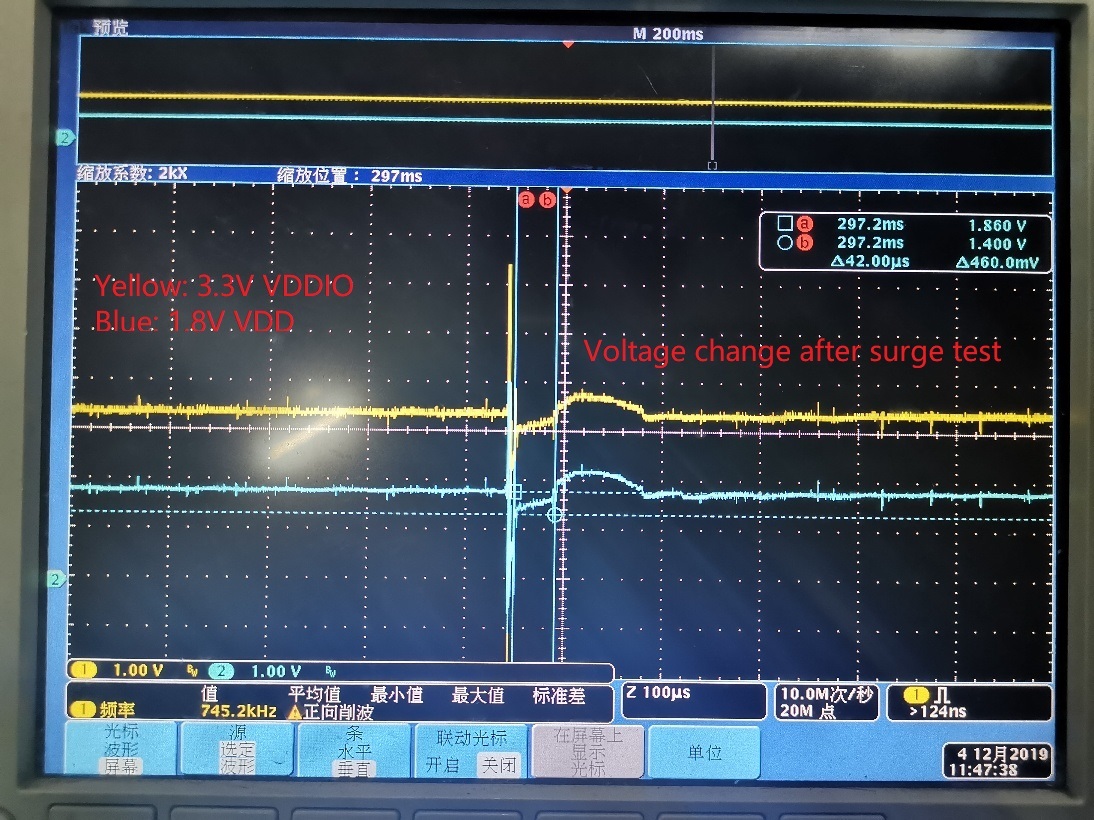

My customer did surge test on their F28034 board, they find the issue that the system frequency will change from 60Mhz to 30Mhz by monitoring XCLKOUT pin as below. actually if we look at what happen when did surge test, there will have voltage overshot at 3.3V and 1.8V as below, and the system frequency will change slowly from 2MHz to 30MHz and then stable at 30MHz. they use the internal clock without external clock circuit.

question is what happen in MCU when did the surge test? is the internal clock fail or the PLL fail?

and in such a big interference, why MCU did not reset or go to NMI interrupt but instead continue to run the code at the frequency of 30MHz, customer also monitor the output of UART communication and find the baud rate also become half of setting value.

do we have any suggestion for customer? I have review the schematic and confirm each Vddio/Vdd pin connected with 2.2uf cap and close to the pin.