Dear Sir ,

we are using the 28376S chip in one of our product under development , and has some issue / questions regrading ADC Acquisition time .

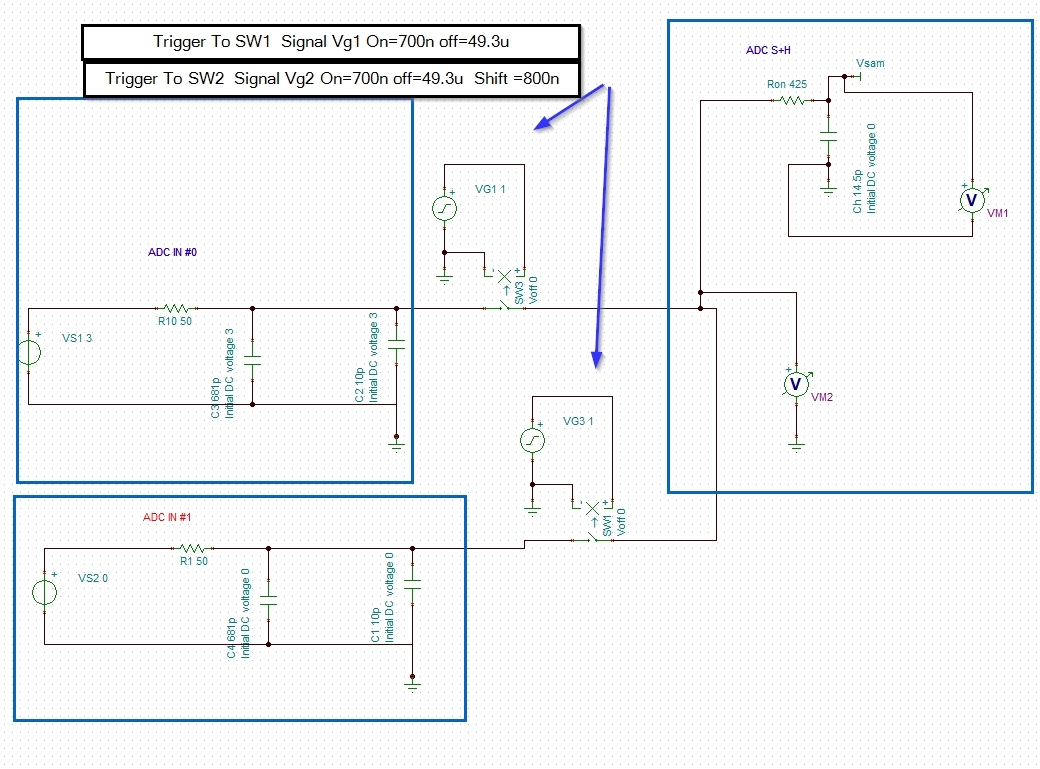

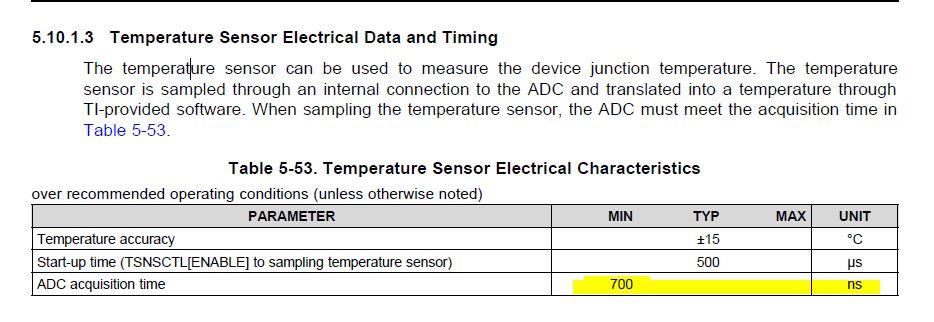

1. the ADC-A is set to work in frequency of 50Mhz (the C28x is working on 200Mhz) , Acquisition time is time to 500ns (i have tried also 1000ns)

2. we have set 4xSOC (0..4) to Sample specific Analog inputs (3,2,5,4,0) - the trigger for the SOC0-4 are from PWM1 (e.g EPMSOCA in frequency of 20Khz)

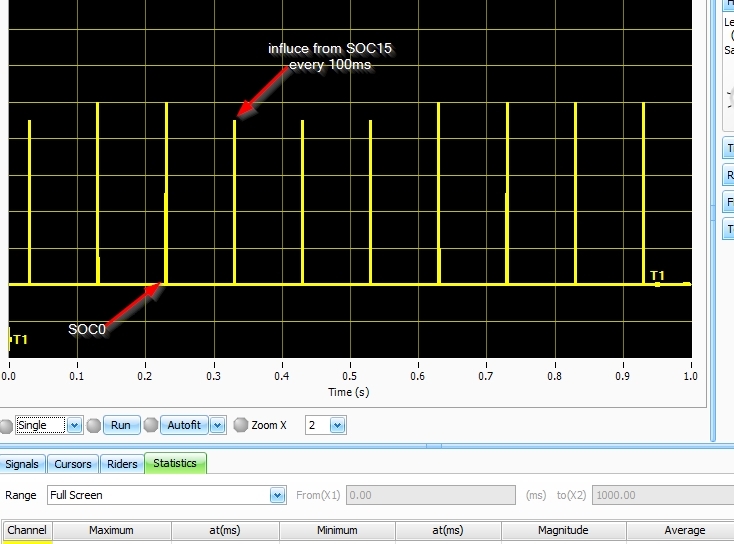

3. we have defined in addition SOC15 to sample Internal temperature (e.g CHSEL=13), the trigger is from software every ~100ms

a. the issue we are facing is that every ~100ms (the internal temperature measurement) there is some influence on SOC0 (which sample right after SOC15 ) , the SOC0 is connected to 0v .

the SOC0 vary around +15 ADC points , if we stop the sample on SOC15 , there is no issue , can you advice on this issue ?

b.regarding ADC Acquisition time if we have on the analog pin RC filter of RS=220 Ohm and CS=680ns the Acquisition time according to the document will be ~ 880ns

is it correct , or we have miscalculate ?

c. what can additionally cause influence between sequential sampling (e.g. SCO0 influence SOC1 , SOC1 influence SOC2 )

we are suspecting that it is due to sequential sampling and not noise , please your opinion ?