Part Number: TMS320F28069

Hi expert,

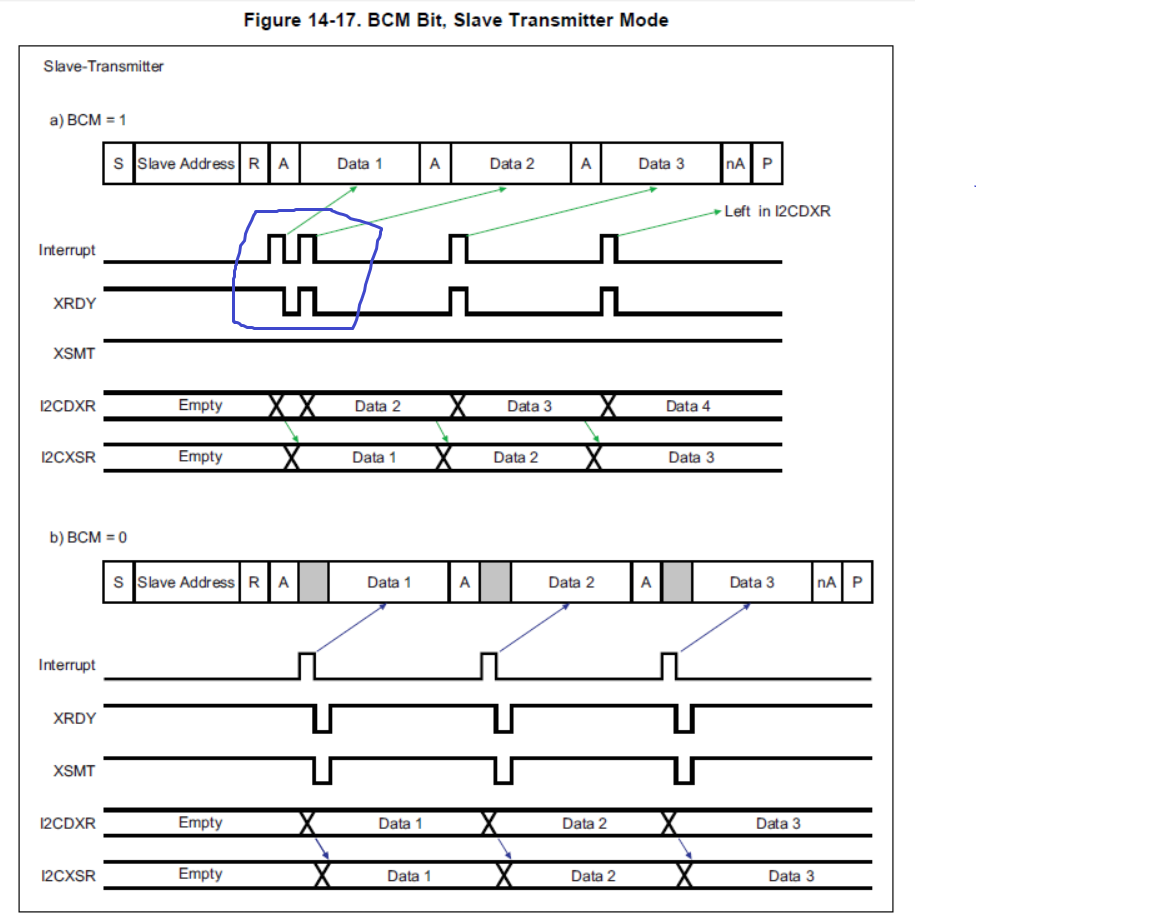

I'd like to know the function of I2CEMDR register and its BCM bit. In IIC slave mode, is that bit a switch for enabling or disabling IIC clock stretching?

From 14.2.7 Clock Synchronization in TRM, I think F28069 device can stretch IIC clock in slave mode by default, am I correct?

If some case we set BCM to 1 and device is in IIC slave mode, will it stretch SCL to 0 if not data is put into I2CDXR in time?

Please help with these three questions.

Thanks

Sheldon