Part Number: TMS320F28388D

Other Parts Discussed in Thread: C2000WARE

Hi,

I am using the ControlCARD to implement a EtherCAT slave stack. The software is based from \ti\c2000\C2000Ware_2_01_00_00\libraries\communications\Ethercat\f2838x\examples\f2838x_cm_echoback_solution. The test result with "Free run" mode is ok, but it failed with "DC Sync0 mode".

When EtherCAT enters Safe-Op state with DC Sync0 mode, the SYNC0 event should happen cyclically. However, it didn't happen. The raw status of SYNC0(ESCSS_INTR_RIS Register) is always zero. And the CM never enters the SYNC0 ISR.

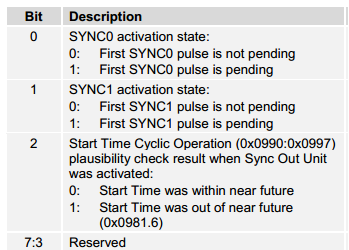

I also checked the ESC register through TwinCAT as below. The 0x0980 and 0x0981 register were correct. And I found that ESC register 0x0984.Bit0=1, which means that the first SYNC0 pulse was pending.

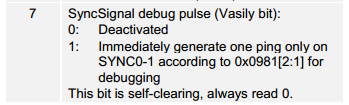

Then, I changed the ESC register 0x0981.Bit7 from 0 to 1 through TwinCAT, the CM entered SYNC0 interrupt routine correctly.

Also, if I forced the Register ESCSS_INTR_SET.SYNC0_SET to 1, the CM entered SYNC0 interrupt routine as well.

So, in this case, i think the SYNC0 event is missing. Is there any way to confirm that? Or is there an example project with DC sync0 mode tested?