Dear C2000 expert,

I'm currently using F280049 to design a power module. Due to there is a isolation between MCU and sensed signals, a extern adc with isolator was used, and the adc result will be sent to F280049 through SPI interface.

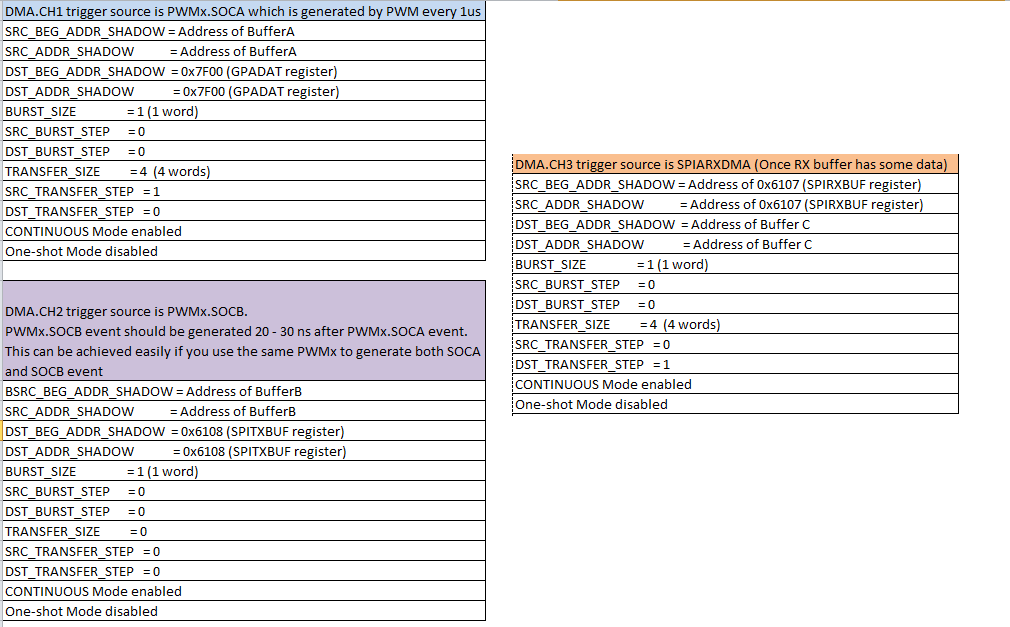

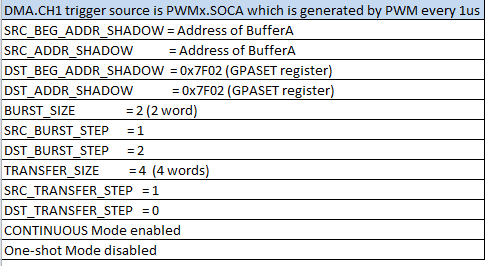

Below picture shows the diagram of F280049 and 4 external adcs. F280049 is SPI master, and the 4 adcs are SPI slavers. And CS signal was controled by different GPIOs in F280049, I'd like to get the all 4 adcs result in one switch cycle, because all those signals are used as feedbacks for control loop, can you please share some suggestions?

I don't want take much CPU usages due to the switch frequency is 200KHZ. The conversion speed of ADC is very fast, the adc was triggered to start conversion by CS signal pull low.

If there are some ways of triggering spi to read external adcs automatically without CPU intervention, that would be perfect. Thanks