Other Parts Discussed in Thread: CONTROLSUITE

Tool/software: Code Composer Studio

Hi all:

I'm reading the source code:D:\ti\controlSUITE\development_kits\TMDSHVRESLLCKIT_v1.0\HVLLC

I got a problem at build 3: when does the SR turn off?

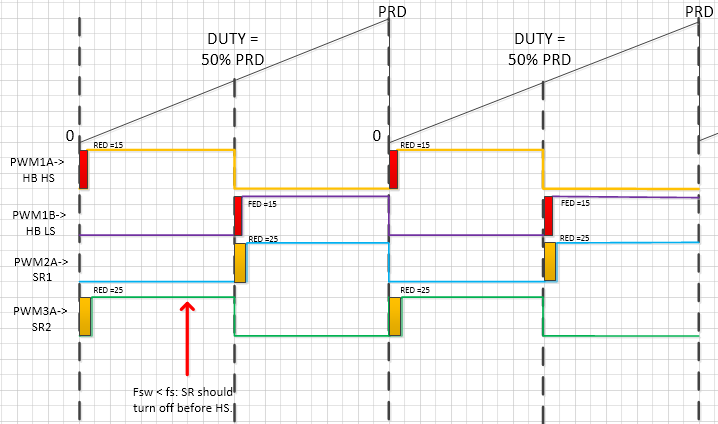

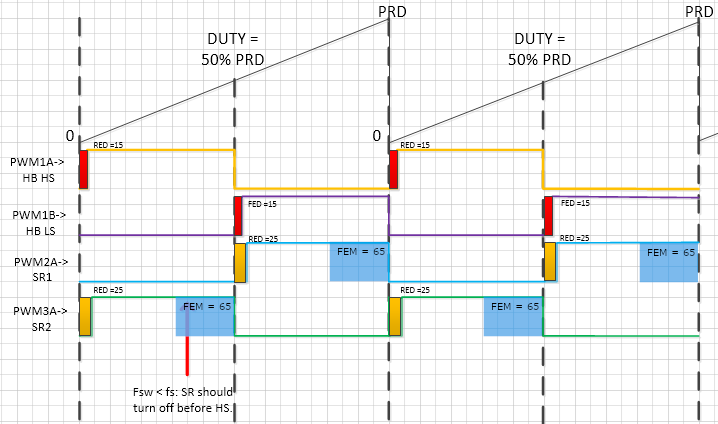

1) The SR PWM3A ON/OFF is initialized same to the HB HS PWM1A(ZERO = SET, COMPA = clear); the SR PWM2A is same to the HB HS PWM1B.

2) The Analog Comparators is initialized as below:

// Configure ePWM Trip-Zone module

EPwm2Regs.TZCTL.bit.DCAEVT1 = TZ_FORCE_HI; // EPWM2A will go HIGH

EPwm3Regs.TZCTL.bit.DCAEVT1 = TZ_FORCE_HI; // EPWM3A will go HIGH

It means the SR will turn on when SR current is greater than the value of DACVAL.

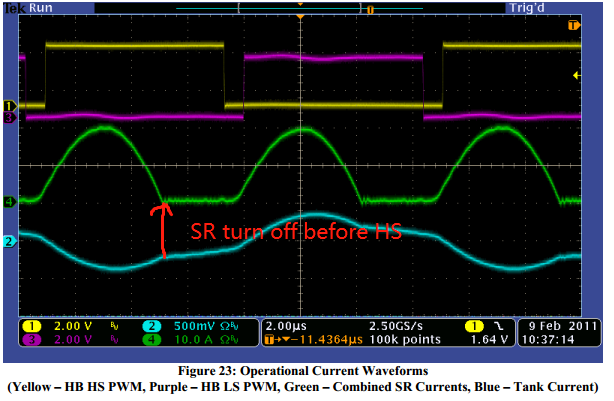

3)The SR PWM should be turn off before the HB HS PWM when fsw < fs. This is show in the Figure 23 of "HVLLC-SWGuide.pdf"

Problem: Who turn off the SR PWM before the HB HS PWM when fsw < fs?

Looking forward to your reply. Thank you!