Hi Team,

My customer face an issue that in their application code sometimes cannot enter ADC interrupt. here are the details of the issue:

The ADC is trigger per 42us, and then go to ADC interrupt after finish ADC sample. in their main code, there will have a while(1) function that enable global interrupt for 3ms and disable interrupt for 6ms, so in these 6ms that disable global, there will not have ADC interrupt. but in the period of during 3ms, there will have ADC interrupt,

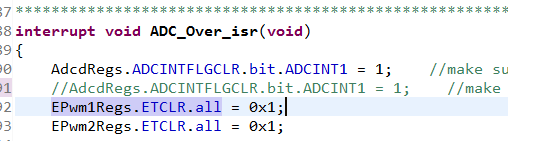

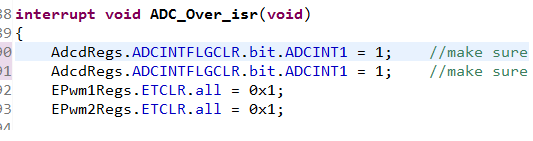

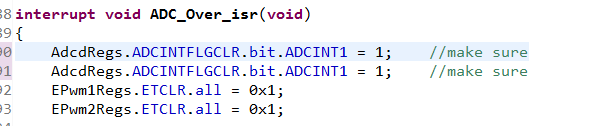

in the interrupt there will have code to clear the interrupt flag.

at the beginning everything is ok, but when run the code for several seconds, the code will never enter ADC interrupt again, both the ADC sample and the code run in the main function are both ok, and we see from the ccs window that the ADC interrupt flag was not clear. if clear the ADC interrupt by manual in ccs window, then ADC interrupt can be accessed for several seconds , but after these several seconds then will never enter ADC interrupt again.

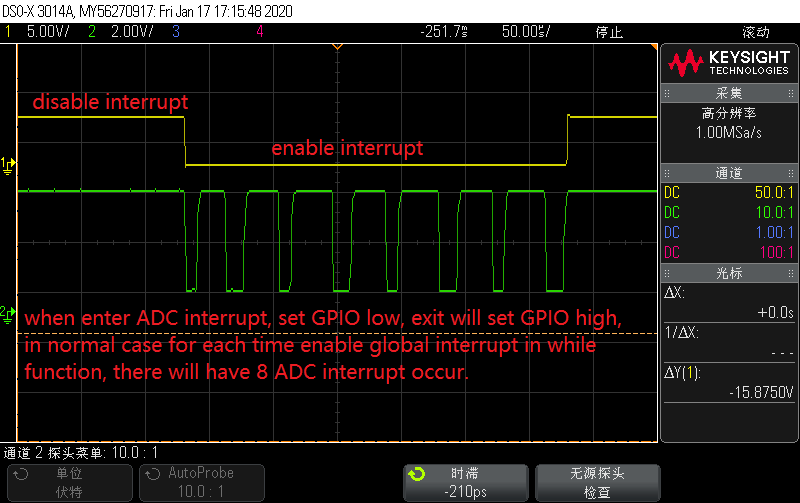

we use GPIO toggle to see exactly what happen and if any conflict. as below show yellow waveform show the time to enable the interrupt. green show if ADC interrupt happen. in normal case at the beginning the waveform is below:

then we capture the waveform when start to have issue as below:

we also capture the previous waveform of the issue happen below:

we guess there are two interrupt request almost at the same time when issue occur although in normal case the interrupt is trigger per 42us. when first interrupt occur, and enter the interrupt service code, there will have code to clear the interrupt flag. but at the same time the second interrupt occur and this interrupt flag was not clear, then the code will never enter the interrupt service code again.

in order to verify this, we add one line code in the interrupt to clear the interrupt flag as below showed, so there are two line code to clear the interrupt flag twice,

it works and the issue is fixed.

question is what we guess is true and any principle to explain the phenomenon above? any suggestion for the case that need to disable and reenable global interrupt in the while(1) function?