Other Parts Discussed in Thread: C2000WARE

Dear all,

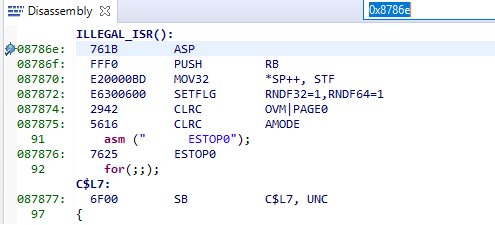

We reset the DSP with watchdog module. Stepping the code, we see that just after the line "WDCR[WDCHK] = 0", the execution jumps to "ILLEGAL_ISR (ITRAP0)".

Of course, the DSP is reset but, is this the normal behavior?

Best regards and thank you.

Paloma