Hi team:

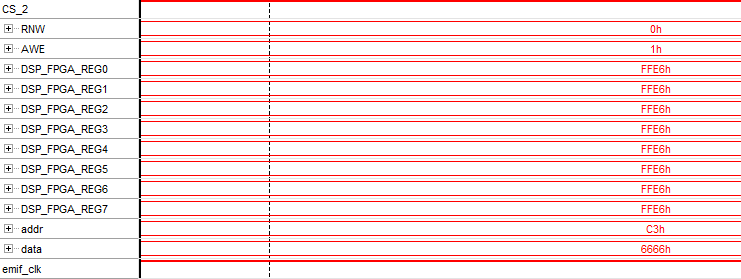

When I use F28377d to access CS2 area through EMIF, the output address is incorrect,and CS2 is not pulled down, RNW and WE signals are not correct.

I have followed the manual, replaced A0 with EMxBA1, and then connected [A7: A1] to [A6: A0]. The code and screenshot are attached below for some ideas.

#include "F28x_Project.h"

void main(void)

{

InitSysCtrl();

EALLOW;

ClkCfgRegs.PERCLKDIVSEL.bit.EMIF1CLKDIV = 1; // PLLSYSCLK 1/2 for EMIF

EDIS;

InitGpio();

EALLOW;

//led

GpioCtrlRegs.GPEMUX1.bit.GPIO133=0;

GpioCtrlRegs.GPEDIR.bit.GPIO133=1;

//cs2 rd we

GpioCtrlRegs.GPBMUX1.bit.GPIO32=2; //cs0 LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO34=2; //cs2 LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO33=2; //RNW HIGH ENABLE

GpioCtrlRegs.GPAMUX2.bit.GPIO31=2; //WE LOW ENABLE

GpioCtrlRegs.GPBMUX1.bit.GPIO37=2; //EM1OE LOW ENABLE

//addr

GpioCtrlRegs.GPCMUX2.bit.GPIO92=3; //EM1BA1

GpioCtrlRegs.GPBMUX1.bit.GPIO38=2; //A0

GpioCtrlRegs.GPBMUX1.bit.GPIO39=2; //A1

GpioCtrlRegs.GPBMUX1.bit.GPIO40=2; //A2

GpioCtrlRegs.GPBMUX1.bit.GPIO41=2; //A3

GpioCtrlRegs.GPBMUX1.bit.GPIO44=2; //A4

GpioCtrlRegs.GPBMUX1.bit.GPIO45=2; //A5

GpioCtrlRegs.GPBMUX1.bit.GPIO46=2; //A6

GpioCtrlRegs.GPBMUX1.bit.GPIO47=2; //A7

GpioCtrlRegs.GPBMUX2.bit.GPIO48=2; //A8

GpioCtrlRegs.GPBMUX2.bit.GPIO49=2; //A9

GpioCtrlRegs.GPBMUX2.bit.GPIO50=2; //A10

GpioCtrlRegs.GPBMUX2.bit.GPIO51=2; //A11

GpioCtrlRegs.GPBMUX2.bit.GPIO52=2; //A12

GpioCtrlRegs.GPCMUX2.bit.GPIO86=2; //A13

GpioCtrlRegs.GPCMUX2.bit.GPIO87=2; //A14

GpioCtrlRegs.GPCMUX2.bit.GPIO88=2; //A15

GpioCtrlRegs.GPCMUX2.bit.GPIO89=2; //A16

GpioCtrlRegs.GPCMUX2.bit.GPIO90=2; //A17

GpioCtrlRegs.GPCMUX2.bit.GPIO91=2; //A18

//GpioCtrlRegs.GPCMUX2.bit.GPIO92=2; //A19

//data

GpioCtrlRegs.GPCMUX1.bit.GPIO69=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO70=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO71=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO72=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO73=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO74=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO75=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO76=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO77=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO78=2;

GpioCtrlRegs.GPCMUX1.bit.GPIO79=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO80=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO81=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO82=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO83=2;

GpioCtrlRegs.GPCMUX2.bit.GPIO85=2;

EDIS;

Emif1Regs.ASYNC_CS2_CR.all = (EMIF_ASYNC_ASIZE_16 | //16位内存

EMIF_ASYNC_TA_4 | //Turn Around

EMIF_ASYNC_RHOLD_8 | //读保持时间

EMIF_ASYNC_RSTROBE_64 | //读选通 时间

EMIF_ASYNC_RSETUP_16 | //读建立时间

EMIF_ASYNC_WHOLD_8 | //写保持时间

EMIF_ASYNC_WSTROBE_64 | //写选通时间

EMIF_ASYNC_WSETUP_16 | //写建立时间

EMIF_ASYNC_EW_DISABLE | //拓展等待禁用

EMIF_ASYNC_SS_DISABLE); //strobe select模式禁用

DINT;

InitPieCtrl();

IER = 0x0000;

IFR = 0x0000;

InitPieVectTable();

EINT;

int i;

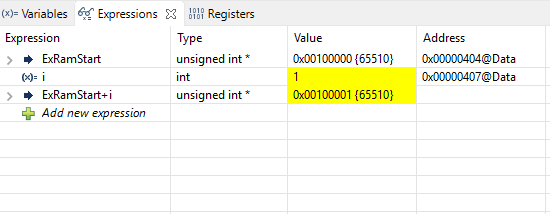

Uint16 *ExRamStart = (Uint16*)0x00100000;

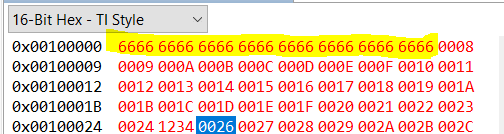

for(i=0; i<0x0008; i++)

{

*(ExRamStart+i)=0x6666;

}

while(1)

{

GpioDataRegs.GPECLEAR.bit.GPIO133=1;

DELAY_US (500000);

GpioDataRegs.GPESET.bit.GPIO133=1;

DELAY_US (500000);

}

}

The hardware is normal, I have tested under GPIO mode.

I did a single step debugging in the "for" loop. I put 6663, 6666, 6669 to the address of 0000, 0001, 0002 respectively. I found that no data was put on the data bus during the loop. When the “for” loop is ended and the “while” loop is entered, the last data (6669h), is output to the data bus. At this time, the address line outputs C3h. I've already referred to the official routine, and I don't know if I've missed any registers?

Best regards